工具与软件:

尊敬的技术支持团队:

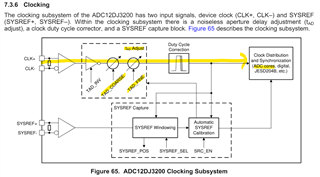

是否可以在 ADC12DJ3200上使用双通道模式(寄存器0x201 =3)来移动和调整 ADC INA 和 ADC INB 之间两个 ADC 的采样时序?

问题1

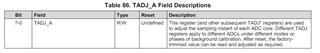

对于采样时序调整寄存器、TADJ_A (0x086)和 TADJ_B (0x089)是否正确?

如果没有、请告知我们合适的寄存器。

问题2

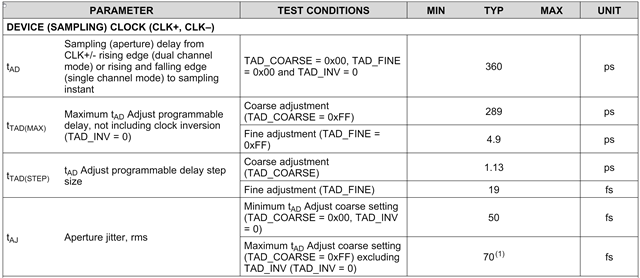

采样计时可以移位多少个 CLK 周期或多少秒?

我在0x86、0x89寄存器页面上找不到该地址

问题3

是否在 CAL_EN (0x061)之前或以不同的顺序存在设置顺序规范?

是否有指定的设置顺序?

8.3初始化设置中有一个常规设置程序、

应采取哪些步骤来设置寄存器以调整采样时序?

...

此致、

TTD