工具与软件:

尊敬的 TI:

我通过 SPI 接口按以下方式配置 ADC3663:

- 写入地址0x07:0x4b

- 写入地址0x13:0x1

- 等待1毫秒

- 写入地址0x13:0x0

- 写入地址0x19:0x10

- 写入地址0x1b:0xc0

应将2线接口配置为16位、并将输出位映射器配置为20位。 我还配置了一个具有以下值0x15555的恒定模式(只有偶数位为1)。

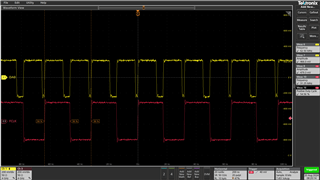

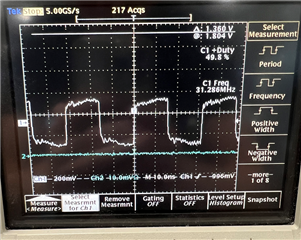

FCLK 和 DA0的信号看起来不错、因为得到的 FCLK 占空比为50/50、数据信号显示10位。 由于我使用的是16位 ADC、因此低2位为0:

不过、在配置 ADC3663时、请遵循以下方式:

- 写入地址0x07:0x4b

- 写入地址0x13:0x1

- 等待1毫秒

- 写入地址0x13:0x0

- 写入地址0x19:0x10

- 写入地址0x1b:0x80

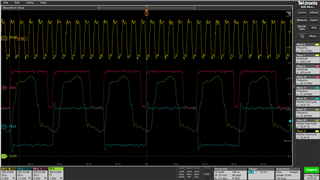

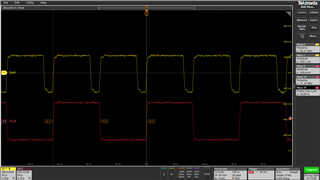

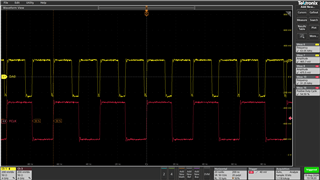

我获得以下信号(也是0x15555的恒定模式):

FCLK (红色信号)的占空比现在为55/45、DA0似乎在9和10位之间切换。 不过、我的预期是、此配置能够产生18位输出、即 FCLK 中每半个周期有9位。

我如何用 FCLK 占空比50/50正确配置18位输出?

此致、

Felix