Other Parts Discussed in Thread: ADS9219EVM, ADS9218, ADS9219

主题中讨论的其他器件: ADS9218、 ADS9219

工具与软件:

尊敬的先生/女士:

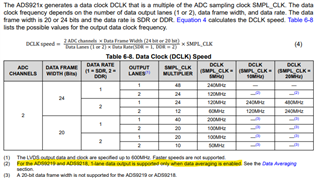

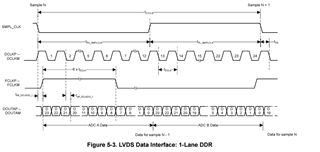

我们目前正在测试 ADS9219EVM。 Ads92xx_EVM_GUI 软件似乎在单通道 DDR 模式上捕获 ads9218数据时自动启用 OSR2滤波器。

这是 ADS9218 ADC 的预期行为吗? 是否可以在单通道 DDR 模式下从 ADS9218 ADC 获取10MSPS 输出?

此致、

Panneer Raja Vajravelu