Other Parts Discussed in Thread: DS90UB947-Q1

主题中讨论的其他器件:DS90UB947-Q1、 DS90UB928Q

工具/软件:

您好的团队、

我想使用 DS90UB947-Q1进行双 LVDS 传输、但我想分离奇数和偶数 CLK。

因此、我想同时使用 DS90UB927Q 和 DS90UB928Q 来进行双 LVDS 传输。

这是可能的吗?

此致、

Ryu。

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Other Parts Discussed in Thread: DS90UB947-Q1

工具/软件:

您好的团队、

我想使用 DS90UB947-Q1进行双 LVDS 传输、但我想分离奇数和偶数 CLK。

因此、我想同时使用 DS90UB927Q 和 DS90UB928Q 来进行双 LVDS 传输。

这是可能的吗?

此致、

Ryu。

您好、Ryu、

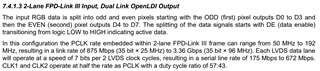

947从源接收视频作为直通。 您可以使用寄存器0x5B 位3来确定您的偶数或奇数是否为主链路或辅助链路。 您可能会看到此处随附的这个示例。

e2e.ti.com/.../1185.947_5F00_Validation_5F00_Odd_5F00_Even_5F00_on_5F00_FPD3.pdf

Aaron

您好、Ryu、

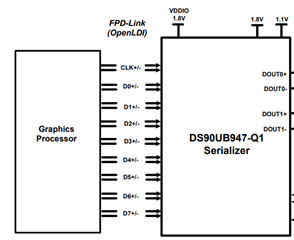

为了阐明 Aaron 的要点、947只具有一个来自 SoC 的 CLK 输入、请参阅下文:

数据通道 D0-D3是通道1 LVDS、而 D4-D7是通道2 LVDS。

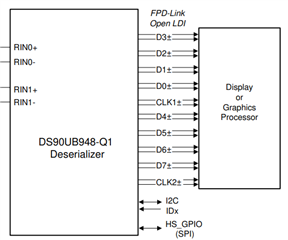

假设 DS90UB948有双 FPD-Link 输入 、对于948上的偶数/奇数分配、它看起来是这样的:

对应于948上的这些引脚排列:

CLK1和 CLK2将以每个 OLDI 端口 PCLK 的一半速率运行、如果您的系统需要将 CLK1 与 CLK2不同、是否有特定的要求?

可以通过947和948之间的 GPIO 使用 PWM 信号、请确保它们是匹配的(例如、947的 GPIO0输入对应于948上的 GPIO0输出)。

此致、

Miguel