工具/软件:

大家好:

我的一个客户考虑将 DP83822H 用于其新产品。

现在、他们有以下问题。

请你给我答复。

Q

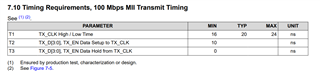

他们考虑 将该器件与 MII 100BASE-TX 搭配使用。

他们 想知道 XI (主时钟输入)和 TX_D[1:0]、TX_EN 信号之间的建立/保持时间。

用户可以找到以下针对 RMII 情况的时序规定。

TX_D[1:0]和 TX_EN 数据设置至 XI 上升

从 XI 上升开始 TX_D[1:0]和 TX_EN 数据保持

但他们并没有针对 MII 情况找到这些规定。

您能告诉我这些设置/保持时间调节值吗?

非常感谢您的答复。

此致、

Kazuya。