Other Parts Discussed in Thread: DS90UB981-Q1, DS90UB928Q-Q1, DS90UB947-Q1

器件型号: DS90UB926Q-Q1

Thread 中讨论的其他器件: DS90UB928Q-Q1、 DS90UB947-Q1、DS90UB981-Q1

工具/软件:

背景:

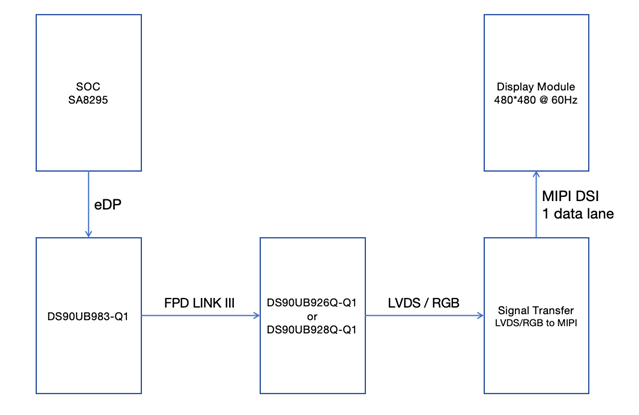

Qualcomm 8295 平台汽车产品需要使用 TI 的 FPD link 芯片。

问题:

我们希望使用 DS90UB928Q-Q1 来使用 FPD 链路 III。但是、当前 480 * 480 的屏幕分辨率不足以满足 FPD 链路 III 对 PCLK>25M 的要求

如果分辨率提高到 584 * 720 分辨率、则可能满足 PCLK>25M 标准、但估计的 MIPI 速率超过 500Mbps、并且不符合显示模块的要求。

我想问是否有任何解决办法来解决这个问题。