主题中讨论的其他器件:AM4376、

- 在设计中将 DP83822H PHY 与 AM4376一起用作 MAC

- 问题似乎与温度有关(发生时随温度升高)。 在 Ta =+70°C 时进行测试、DP83822H 时的 TC < 90°C

- 上电时偶尔出现意外的捆扎信息(由于温度、输入泄漏等原因)的第一个假设尚无法确认( 上电后、捆扎寄存器的读数一致、如果链路丢失、读数也不相同。

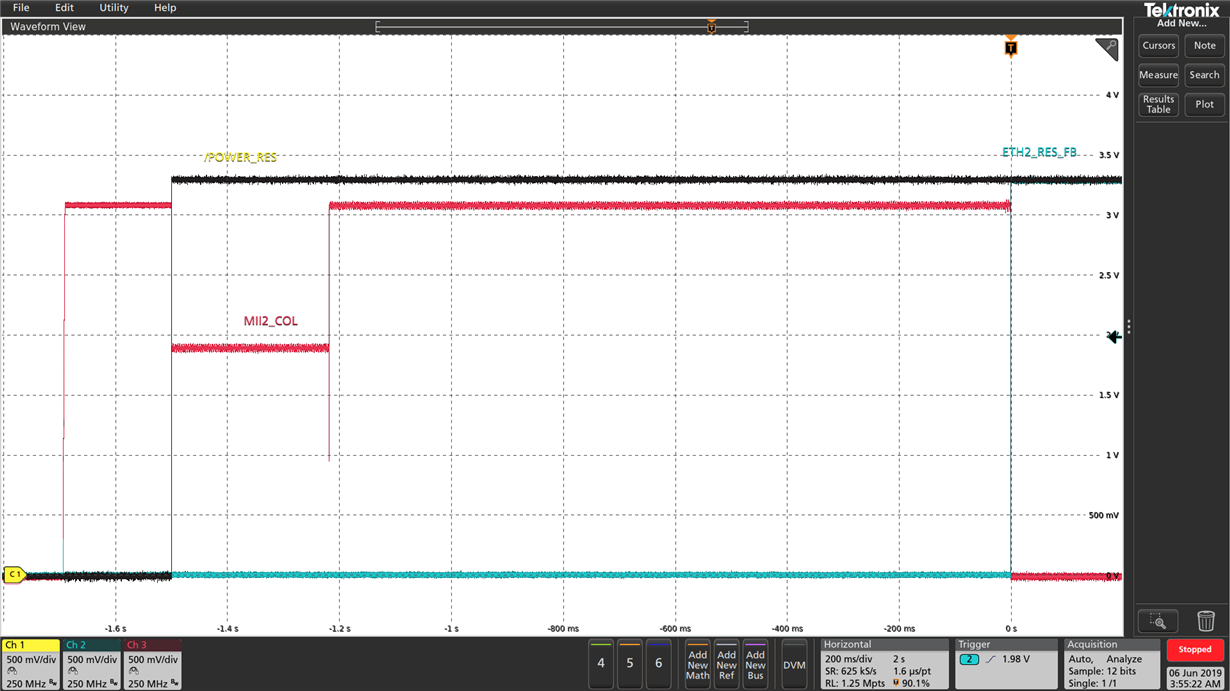

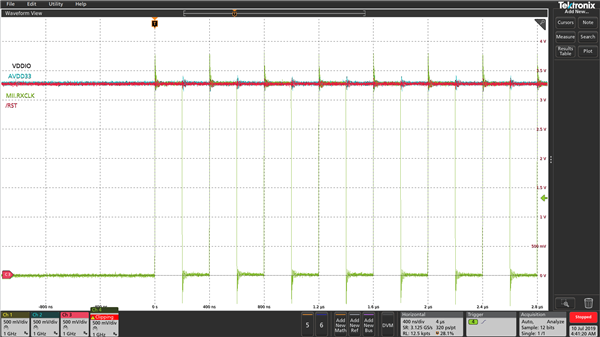

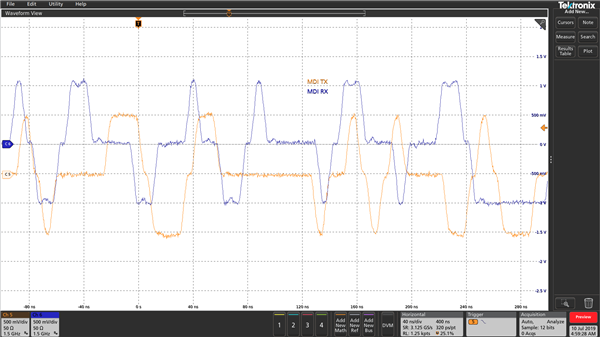

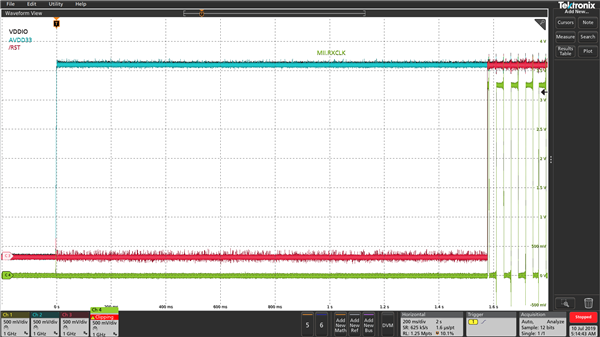

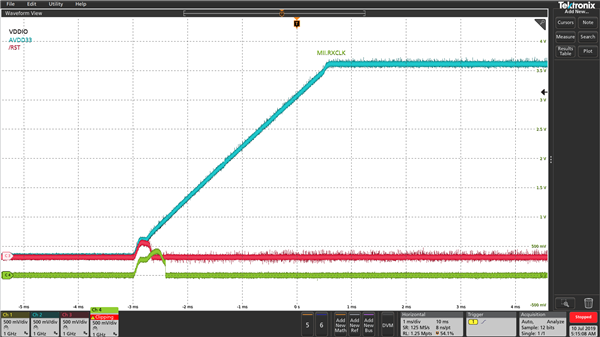

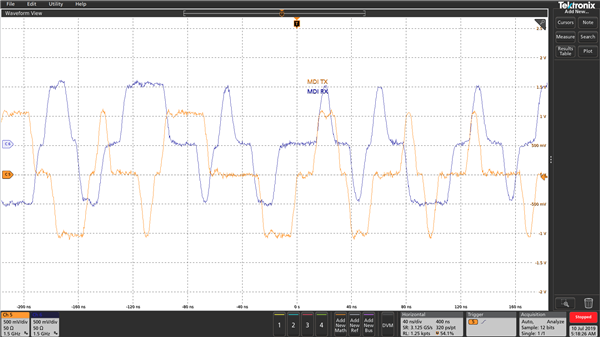

- 下面的示波器图显示了 Ta = 25°C 时的引导时序 MII2_COL 用于监控、因为搭接电平会影响 PHY 地址位0和 PHY 模式(模式2和3 = FX_EN、光纤模式)

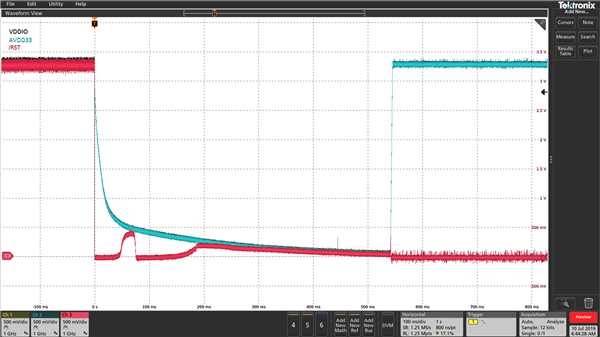

- 上电时、MII2_COL 内部上拉。 大约200ms 后、释放/power_RES、启动 MAC 进行引导(第一级、MII2_COL <2V、第二级、MII2_COL、内部 PU <3、3V)

- MII2_COL 纹波~200mV 低于 VDD 的原因应该是输入泄漏和内部 PU 产生的压降、但电平应处于预期的搭接模式4 (2、29V...3、3V)内。 MII2_COL 处没有外部 PU/PD 电阻器。

- 在第2个引导阶段结束时、释放 PHY 复位(浅蓝色)、并且 PHY 将更改为工作模式、从而将 MII2_COL 驱动为低电平。

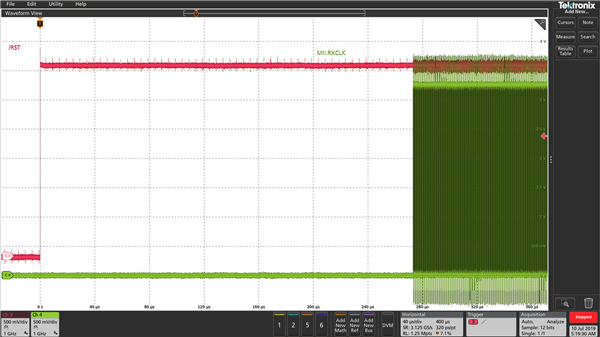

- 未显示(但已验证)、第一次 MDIO 访问在 PHY 复位释放后不到200ms 开始(MDC 在复位后启动200、1ms)

- 从数据表中的时序图中可以看出、这并不清楚、哪一个图适用于所显示的启动阶段以及在锁存引脚的时间点

- 数据表(第8.5.1节)显示:"这些引脚的值在 powr up 或硬件复位时进行采样"、显示了两个图(图1、加电时序和图2、复位时序)

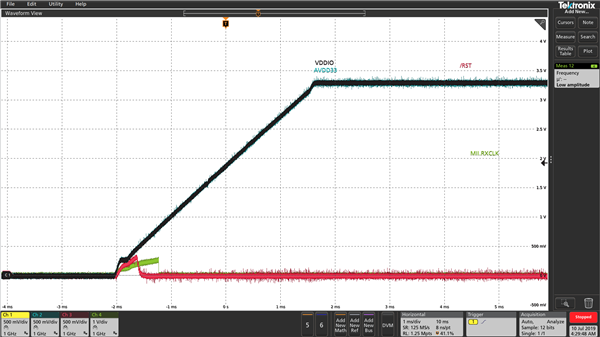

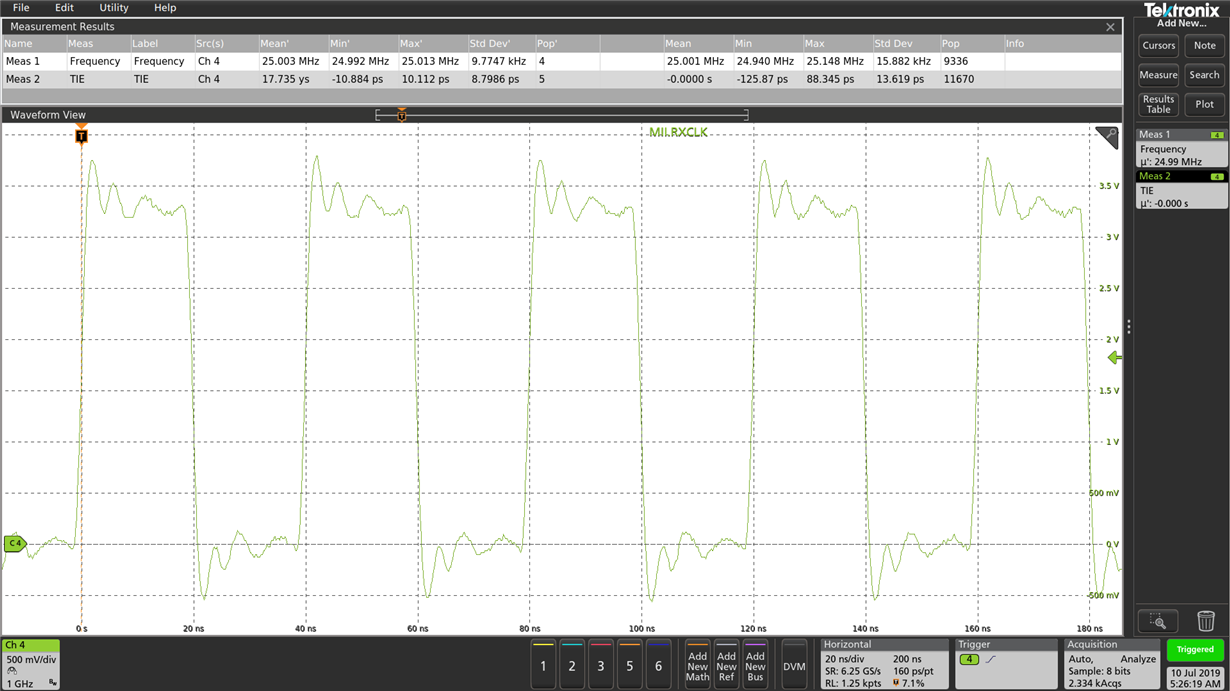

- 在这两个图中,PHY 时钟在电源斜升之前已经处于活动状态。

- 在上电图(图1)中、复位在电源斜升的同时释放、这与上面介绍的引导序列不同。 以下哪种时序图适用????

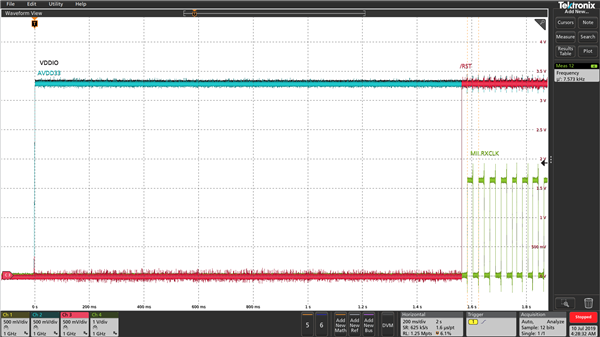

- T2 =最大值 复位释放后200ms、复位释放后 MDC 保持前的上电稳定时间(此处未显示、但已验证)

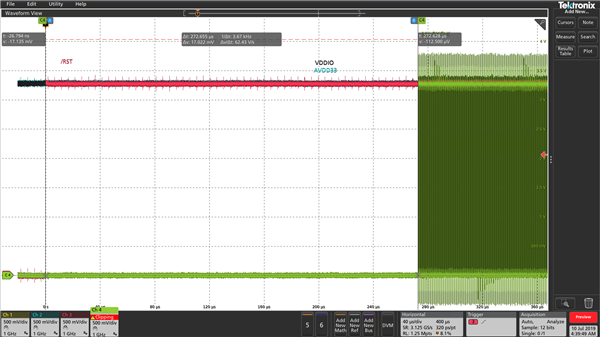

- T3 =典型值 复位释放后用于上电的200ms 硬件配置锁存时间在这里不能有效、因为此时 PHY 主动将 MII2_COL 驱动为低电平。 这意味着闩锁必须是以前的,但在哪里???

- T4 =典型值 在锁存后64ns、输出驱动器开始工作、将 MII2_COL 驱动为低电平。 这还表明、在所呈现序列中的复位释放后、锁定不能为200ms