您好!

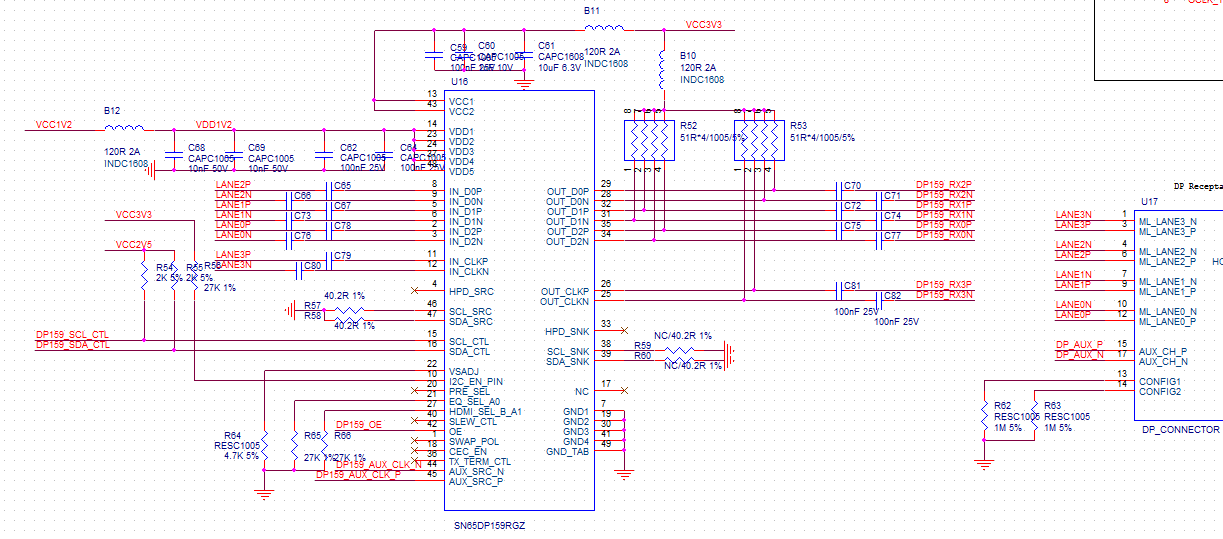

我的项目使用 DP159作为 DisplayPort 重定时器、FPGA 是 Xilinx XC7Z015。 我在 设计中使用 DisplayPort RX 子系统 v2.1,该驱动程序由 Xilinx SDK 提供,但是链路训练始终失败,OUT_clkp/OUT_clkn 没有参考时钟输出。

GPU 为 nVidia GTX1080,当程序运行时,dp159变得很热.... dp159封装标记为 TI 77I AOGO G4。

(a)它 是否与 dp159器件修订版有关?

(b)如 slla358所述、HPD 有两种可能的实现方式:围绕 DP159布线的 HPD 或通过 DP159布线的 HDP、我的板选择围绕 HPD 布线。

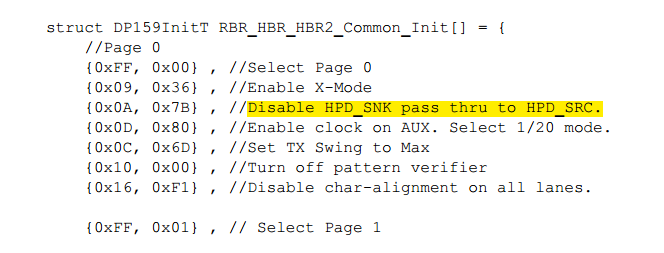

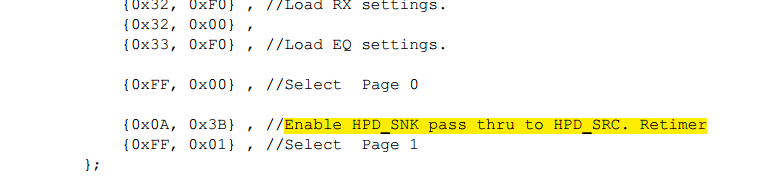

但软件初始 过程首先禁用 HPD 直通、然后通过 DP159启用 HPD。 是否可以推荐 {0x0A、0x3B}?

(b) /* DP159初始化*/

{0xFF、0x00}、

{0x09、0x36}、

{0x0A、0x7B}、

{0x0D、0x80}、

{0x0C、0x6D}、

{0x10、0x00}、

{0x16、0xF1}、

{0xFF、0x01}、

{0x00、0x02}、

{0x04、0x80}、

{0x05、0x00}、

{0x08、0x00}、

{0x0D、0x02}、

{0x0E、0x03}、

{0x01、0x01}、

{0x02、0x3F}、

{0x0B、0x33}、

{0xA1、0x02}、

{0xA4、0x02}、

{0x10、0xF0}、

{0x11、0x30}、

{0x14、0x00}、

{0x12、0x03}、

{0x13、0xFF}、

{0x13、0x00}、

{0x30、0xE0}、

{0x32、0x00}、

{0x31、0x00}、

{0x4D、0x08}、

{0x4C、0x01}、

{0x34、0x01}、

{0x32、0xF0}、

{0x32、0x00}、

{0x33、0xF0}、

{0xFF、0x00}、

{0x0A、0x3B}、

{0xFF、0x01}

(C)/*链接培训*/

switch (ConfigType){

案例 XDPRXSS_DP159_CT_TP1:

/*启用带隙、禁用 PLL、清除 A_LOCK_OVR */

XDpRxSS_Dp159Write (InstancePtr、XDPRXSS_DP159_IIC_SLAVE、

0x00、0x02);

/* CP_EN = PLL (基准)模式*/

XDpRxSS_Dp159Write (InstancePtr、XDPRXSS_DP159_IIC_SLAVE、

0x01、0x01);

/*设置 PLL 控制*/

XDpRxSS_Dp159Write (InstancePtr、XDPRXSS_DP159_IIC_SLAVE、

0x0B、0x33);

/*设置 CP_CURRENT */

XDpRxSS_Dp159Write (InstancePtr、XDPRXSS_DP159_IIC_SLAVE、

0x02、0x3F);

LCount =(LaneCount = XDPRXSS_DP159_lane 计数_1)?

0xE1:(LaneCount == XDPRXSS_DP159_lan_count_2)?

0xC3:0x0F;

LRate =(LinkRate == XDPRXSS_DP159_HBR2)? 0x0:

(LinkRate =XDPRXSS_DP159_HBR)? 0x1:0x2;

/*启用 RX 通道*/

XDpRxSS_Dp159Write (InstancePtr、XDPRXSS_DP159_IIC_SLAVE、

0x30、LCount);

/*启用带隙、启用 PLL、清除 A_LOCK_OVR */

XDpRxSS_Dp159Write (InstancePtr、XDPRXSS_DP159_IIC_SLAVE、

0x00、0x03);

/*启用固定 EQ (重置自适应 EQ 逻辑)*/

XDpRxSS_Dp159Write (InstancePtr、XDPRXSS_DP159_IIC_SLAVE、

0x4C、0x01);

/*设置 EQFTC 和 EQLEV (固定 EQ)*/

XDpRxSS_Dp159Write (InstancePtr、XDPRXSS_DP159_IIC_SLAVE、

0x4D、(LRATE << 4)|

(XDPRXSS_DP159_EQ_LEV 和0x0F));

if (LinkRate = XDPRXSS_DP159_HBR2){

CPI = XDPRXSS_DP159_CPI_PD_HBR2;

PllCtrl = XDPRXSS_DP159_PLL_CTRL_PD_HBR2;

}

否则、如果(LinkRate = XDPRXSS_DP159_HBR){

CPI = XDPRXSS_DP159_CPI_PD_HBR;

PllCtrl = XDPRXSS_DP159_PLL_CTRL_PD_HBR;

}

否则{

CPI = XDPRXSS_DP159_CPI_PD_RBR;

PllCtrl = XDPRXSS_DP159_PLL_CTRL_PD_RBR;

}

/*启用 TX 通道*/

XDpRxSS_Dp159Write (InstancePtr、XDPRXSS_DP159_IIC_SLAVE、

0x10、LCount);

/*启用 PLL 和带隙、设置 A_LOCK_OVR 和设置

*展开 LPRES

*

XDpRxSS_Dp159Write (InstancePtr、XDPRXSS_DP159_IIC_SLAVE、

0x00、0x23);

/*等待 PLL 锁定*/

while ((ReadBuf = 0)&&(计数器<

XDPRXSS_DP159_LOCK_WAIT)){

XDpRxSs_Dp159Read (InstancePtr、

XDPRXSS_DP159_IIC_SLAVE、0x00、&ReadBuf);

ReadBuf &= 0x40;/*锁定状态。 *

COUNTER++;

}

/* CP_CURRENT */

XDpRxSS_Dp159Write (InstancePtr、XDPRXSS_DP159_IIC_SLAVE、

0x02、CPI);

/*设置 PLL 控制*/

XDpRxSS_Dp159Write (InstancePtr、XDPRXSS_DP159_IIC_SLAVE、

0x0B、PllCtrl);

/* CP_EN 为 PD 模式*/

XDpRxSS_Dp159Write (InstancePtr、XDPRXSS_DP159_IIC_SLAVE、

0x01、0x02);

/*选择第0*/页

XDpRxSS_Dp159Write (InstancePtr、XDPRXSS_DP159_IIC_SLAVE、

0xFF、0x00);

/*根据#Lanes 设置 DP_TST_EN、锁存 FIFO 错误*/

LCount =(LaneCount = XDPRXSS_DP159_lane 计数_1)?

0x11:(LaneCount =

XDPRXSS_DP159_lane 计数2)?

0x31:0xF1;

XDpRxSS_Dp159Write (InstancePtr、XDPRXSS_DP159_IIC_SLAVE、

0x16、LCount);

//禁用 PV,允许字符对齐和8b10解码到

*运行

*

XDpRxSS_Dp159Write (InstancePtr、XDPRXSS_DP159_IIC_SLAVE、

0x10、0x00);

/*选择第1页*/

XDpRxSS_Dp159Write (InstancePtr、XDPRXSS_DP159_IIC_SLAVE、

0xFF、0x01);

中断;

案例 XDPRXSS_DP159_CT_TP2:

案例 XDPRXSS_DP159_CT_TP3:

/*启用自适应 EQ */

XDpRxSS_Dp159Write (InstancePtr、XDPRXSS_DP159_IIC_SLAVE、

0x4C、0x03);

/*选择第0页*/

XDpRxSS_Dp159Write (InstancePtr、XDPRXSS_DP159_IIC_SLAVE、

0xFF、0x00);

/*清除 BERT 计数器和 TST_INTQ 锁存器--

*在 DP159中自清除

*

XDpRxSS_Dp159Write (InstancePtr、XDPRXSS_DP159_IIC_SLAVE、

0x15、0x18);

/*选择第1页*/

XDpRxSS_Dp159Write (InstancePtr、XDPRXSS_DP159_IIC_SLAVE、

0xFF、0x01);

中断;

}