主题中讨论的其他器件:DSI-Tuner、

您好!

我的 LVDS LCD 面板出现闪烁问题

我遵循 有关序列初始化和 DSI 调谐器的数据表来配置所有寄存器

不幸的是、我仍然存在闪烁的问题

- 图片、36:

CH3 = LVDS_DATA0CH4 = DSI_CLK

- 图片,37到39

CH3 = LVDS_DATA0CH4 = DSI_DATA0

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

您好!

我的 LVDS LCD 面板出现闪烁问题

我遵循 有关序列初始化和 DSI 调谐器的数据表来配置所有寄存器

不幸的是、我仍然存在闪烁的问题

CH3 = LVDS_DATA0CH4 = DSI_CLK

CH3 = LVDS_DATA0CH4 = DSI_DATA0

您好、Charles、

上次我们聊天时、我提供了以下链接、并提供了一些有关未遵循的原始示波器截图初始化序列的输入。

您能否在使能引脚变为高电平以及 DSI_DATA0和 DSI_CLK 的情况下发送示波器屏幕截图、以便我可以验证初始化序列?

您是否还验证了 DSI 输入上的线时间是否满足 LVDS 输出上的线时间?

评估您发送的 DSI 调谐器片段后、我不明白为什么 LVDS_HFP 与 DSI_HFP 不同。 这可能就是输出代码片段给出行时间不匹配估算的原因、这可能会导致闪烁。 您能否验证 DSI_HFP 和 LVDS_HFP?

谢谢。

察赫

您好、Charles、

我没有立即看到您的配置有任何错误。 不过、我很好奇您为什么器件 EN 为高电平、然后依次拉低和高电平。 首次处于 EN =高电平时、DSI 数据未处于 LP11状态。

首先、您可以尝试将器件配置为仅输出如下所示的内部测试模式吗?

您还可以使用 DSI 调谐器将器件配置为输出内部测试图形。 当针对测试图形进行配置时、器件不使用输入 DSI 数据。 它仅使用 DSI CLK 或外部 REFCLK 来根据 LVDS 时序参数在内部生成测试图案。 测试图案如下所示:

如果测试图案与上面的图案一样、那么使用 DSI 数据时出现的任何闪烁都可能是由于 DSI 输入不稳定或来自 DSI 源的输出不正确而导致的。 如果测试图案出现闪烁或颜色不正确(例如白色条带显示为灰色)、则可能未针对显示面板正确配置 LVDS 输出。 检查所使用的显示面板的格式(格式1与格式2)是否正确、LVDS 时序是否处于规格范围内。

您是否还验证了 DSI 输入上的线时间是否满足 LVDS 输出上的线时间?

谢谢。

察赫

尊敬的 Zach:

关于 EN 引脚、这是因为 SN65DSI84芯片中有一个内部上拉电阻器。

因此、当我们为电路板上电时、引脚从低电平变为高电平、并保持高电平、直到 CPU 将 DSI 序列初始化。

这是不是一个错误的方式做?

我们将进行模式测试、并将结果返回给您。

在 DSI 和 LVDS 上的线时间,你具体是什么意思?

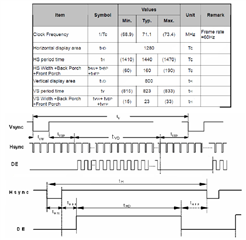

这是不是在下面? 它是否应等于/小于/大于 DSI 调谐器结果? (~20µs)

此致、

查理

Charles

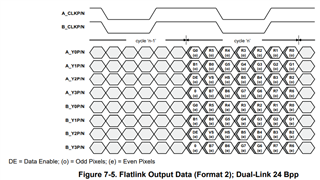

另外、在查看面板规格后、我发现 DSI 调谐器工具还有一个问题。 您需要使用格式2而不是格式1。 要进行验证、您可以将面板的数据表第3.3.3节与 DSI84的数据表第7-5页进行比较。 FlatLink 输出数据(格式2);双链路24 bpp

需要匹配 DSI 和 LVDS 线路时间。 LVDS 输出端的线时间是水平像素总量除以 LVDS 时钟频率。 您可以通过放大数据通道上的数据流来使用示波器测量 DSI 输入端的线时间、如上图所示。 不过、您刚才展示的测量结果似乎是针对 LVDS_DATA0。 您需要将其与 DSI_DATA0进行比较。

谢谢。

察赫

Zach、

我们仅使用1个 LVDS 通道、而不使用2个。 那么为什么需要选择格式2? (0x18=0x7A)

我们更改了寄存器的值、从而得到了良好图形

寄存器值

0x20 0x20

0x21 0x03

0x24 0x00

0x25 0x05

0x2C 0x05

0x2D 0x00

0x30 0x36

0x31 0x00

0x34 0x0F

0x36 0x35

0x38 0x0F

0x3A 0x35

0x3C 0x10

但我们仍有闪烁的问题。。

您好、Charles、

您是否说您正在使用内部测试模式并遇到一些闪烁或变色?

如果是、 测试图案的闪烁或颜色不正确(例如白色条带显示为灰色)、则可能未针对显示面板正确配置 LVDS 输出。 检查所使用的显示面板的格式(格式1与格式2)是否正确、LVDS 时序是否处于规格范围内。

首先、我回顾了您有关该应用的数据表、并注意到您的 HSYNC 和 VSYNC 极性需要设置为正而不是负、如 DSI 调谐器所示。

第二、您是否测量了 LVDS 时钟、您能否验证您在 DSI 调谐器工具中设置的频率实际上是器件输出的频率?

最后、尝试1号和2号后、您可以尝试调整 LVDS 时钟以查看可能对屏幕产生的影响。

谢谢。

察赫

尊敬的 Zach:

不是测试模式、屏幕截图来自正常模式。 (最后一行的像素闪烁)

我配置了寄存器0x18=0x7C (格式2、24bpp)、我可以使用值0x0C 进行测试

是的、 我测量了 LVDS 时钟、我们得到了72MHz (LCD 数据表显示的范围是:68.9MHz 到73.4MHz

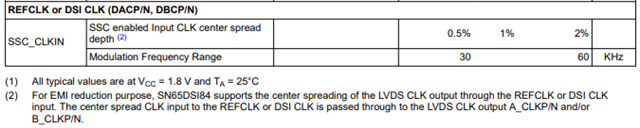

还有一点,我使用 DSI clk 上的扩频,对桥来说是可以的吗? (在数据表中、似乎可以)

谢谢。

查理

Charles

请执行以下操作:

1.您仍然需要使用 HSYNC 和 VSYNC 极性=正极和负极、正如您在 DSI 调谐器中看到的那样。 根据面板的数据表、当 DE 被驱动为高电平时、HSYNC 和 VSYNC 都被驱动为高电平。

2.您是否可以尝试内部测试图案来查看是否有闪烁? 如果没有闪烁、这将有助于缩小 DSI 数据流的问题范围。

3.请验证 DSI 源的视频时序输出是否与您正在对 DSI83/DSI84/DSI85进行编程的输出相匹配。 这包括 DSI CLK 频率、有效像素数据和消隐像素数据。

4.能否测量 DSI_DATA0线时间?

谢谢。

察赫

尊敬的 Zach:

我尝试执行您的4个步骤:

1.可以: HSYNC =负/VSYNC =负/DE =正

2.内部测试图案没有闪烁

3.

通过在 DSI 时钟上使用展频、我们将频率 集中在216MHz、因此我们将寄存器配置为0x12 = 0x2B

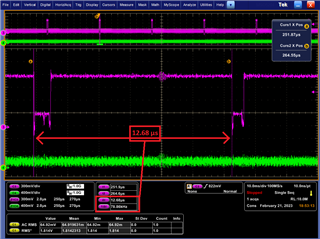

4.在示波器上、我测量了 DSI_DATA0线时间、得到的值= 11.6µs μ s

与 DSI 公式: 线时间=(Htotal * bpp)/(2 * DSI DataLane * DSICLK)= (835*24)/(2 * 4*216MHz)= 11,6µs (参考:"提示 SN65DSI8x -故障排除和技巧")

而对于 LVDS:线时间= Htotal / LVDSCLK = 835 / 72MHz = 11,6µs μ s

您知道 DSICLK 上的扩频功能是否是一个好选择吗?

谢谢。

查理

您好、Charles、

由于内部测试图案测试图案没有闪烁 、因此使用 DSI 数据时出现的闪烁可能是由于 DSI 输入不稳定或来自 DSI 源的输出不正确而导致的。

展频时钟(如数据表中所示为 SSC) 最适合需要关注 EMI 但 SSC 会给您的时钟增加一些抖动的应用。

看看您的直方图、我看到您将频谱扩展得相当宽。 频谱通常应展频为1%。 对于时钟、此频率约为213.84MHz 至218.16MHz。

谢谢。

察赫

尊敬的 Zach:

感谢您的答复

我们的内部测试图案没有闪烁。 但是,您能告诉我需要配置哪个寄存器吗? 以确保做正确的事情。

我们发送了这些寄存器:

i2cset -y -f 2 0x2C 0x20 0x20

i2cset -y -f 2 0x2C 0x21 0x03

i2cset -y -f 2 0x2C 0x24 0x00

i2cset -y -f 2 0x2C 0x25 0x05

i2cset -y -f 2 0x2C 0x2C 0x0A

i2cset -y -f 2 0x2C 0x2D 0x00

i2cset -y -f 2 0x2C 0x30 0x36

i2cset -y -f 2 0x2C 0x31 0x00

i2cset -y -f 2 0x2C 0x34 0x0F

i2cset -y -f 2 0x2C 0x36 0x35

i2cset -y -f 2 0x2C 0x38 0x0F

i2cset -y -f 2 0x2C 0x3A 0x35

i2cset -y -f 2 0x2C 0x3C 0x10

不过、当我们接下来发送时、寄存器0x18 = 0x1A 或1C、该条带为白色1A、灰色为1C。

写入(初始化序列) 0x18=0x1A 时、屏幕颜色错误、但写入1C 时、屏幕颜色正确

我们的寄存器配置:

09 = 00

0A = 05

0b = 10

0d = 00

10 = 26

11 = 00

12 = 2B

13 = 00

18 = 1A

19 = 0A

1A = 00

1b = 33

20 = 20

21 = 03

22 = 00

23 = 00

24 = 00

25 = 05

26 = 00

27 = 30

28 = 21

29 = 00

2A = 00

2b = 00

2C = 0A

2d = 00

2E = 00

2f = 00

30 = 36

31 = 00

32 = 00

33 = 00

34 = 0F

35 = 00

36 = 35

37 = 00

38 = 0F

39 = 00

3A = 35

3B = 00

3c = 00

3D = 00

3E = 00

0d = 01

09 = 01

在这种配置下,仍然有闪烁,你有什么建议吗? 我需要更改什么吗?

谢谢。

查理

您好、Charles、

如果测试图案出现闪烁或颜色不正确(例如白色条带显示为灰色)、则可能未针对显示面板正确配置 LVDS 输出。 检查所使用的显示面板的格式(格式1与格式2)是否正确、LVDS 时序是否处于规格范围内。

根据我在上面所说的内容、您超出了 DSI CLK 的频谱最大展频范围。 频谱通常应展频为1%、展频最大为2%。 您需要处于 大约 213.84 MHz 至 218.16 MHz 的范围内 。

谢谢。

察赫

大家好、Zach、

实际上、我们在外面、我们尝试减少或禁用展频。

但是、在内部测试图案中、我们没有看到闪烁。

如果我们看不到内部测试模式的闪烁,我们应该看不到正常模式下的闪烁,对吗?

关于格式1与格式2、低于我们的 LCD 规范(简短描述):

在 SN65DSI84数据表中,对于一个配置为24bpp 和 MSB 在通道3上的 LVDS 输出,只有一个双链路可能性...

我需要在双链路上配置输出并发送两倍的图片(2x (800x1280)像素)吗? 还是那只是一个图示?

谢谢!

查理

Charles

让我扼要重述到目前为止我们的故障排除中的内容:

-我们已检查您是否使用 DSI 调谐器正确配置了设备

-我们已检查 LVDS 时序参数(时钟频率等)是否在您的显示面板的规格范围内。

-已验证您是否获得了如下所示的内部测试模式:

-您在 DSI 输入上检查了脉冲/线时间。 您已确保 DSI 输入端的线时间(从 HSYNC 到 HSYNC 的时间)与 LVDS 输出端的线时间相匹配。

由此、我们缩小了闪烁的可能原因:

由于测试图案与上面的图案一样、因此使用 DSI 数据时出现的任何闪烁都可能是由于 DSI 输入不稳定或来自 DSI 源的输出不正确而导致的。

由于您使用的是扩频时钟、因此 DSI 时钟仍然会成为 问题、因为如果线路时间匹配、时钟抖动可能会成为问题。

您还可以尝试使用一个干净的外部 REFCLK 作为 PLL 的时钟源、而不是使用 DSI CLK 作为 PLL 源、因为噪声过大的 DSI CLK 可能导致 LVDS 时钟输出不稳定。

谢谢。

察赫

Zach、

但仍有闪烁

然而、我查阅了振荡器的数据表、它被写入的上升和下降时间最大值为3ns ... 我检查了振荡、得到了2ns 和3ns 之间的上升和下降时间

根据 SN54DSI84的数据表、上升和下降时间必须介于100ps 和1ns 之间

我是否需要更改振荡器的基准? 或者我需要更改寄存器的其他内容吗?

内部测试图案清洁

DSI 数据的线时间: 11,56µs μ s

LVDS 的线时间:水平总计/ F_LVDS = 834 / 72 MHz = 11、58MHz

寄存器:0x0A = 0x04/0x0B = 0x00

谢谢。

查理