主题中讨论的其他器件: TMDX654IDKEVM、 TMDS64EVM

工具与软件:

您好!

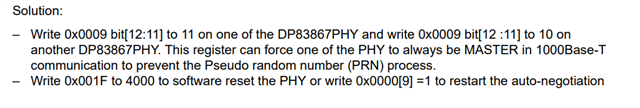

我遇到了 DP83867IR PHY 的链路连接问题、我想最新的应用手册 疑难解答指南(修订版 C)中已经对其进行了介绍。

我的情况似乎与第3.5段第三个要点("读取寄存器0x0005[15]和如果0x0005位[15]= 1")中描述的情况相同。 我只是说"似乎"、因为我仍然无法按照建议读取寄存器0x0005、但行为看起来是相同的。 我确实有两个不同的板、使用此 PHY、但在通过此 PHY 管理的网络进行连接时出现问题。

我正在努力针对 RTOS 所使用的驱动器实施建议的解决方案、但我希望了解所报告信息的更多详细信息。 其中(在应用手册上)显示"PRN 不是完全随机的、如果两个 DP83867同时启动自动协商、则 DP83867可能都发送完全相同的随机种子(PRN)并导致死锁。" 这看起来与我的设置非常相似、因为当电路板同时加电时、问题出现的频率更高。 然而,不是很清楚" 同时" 是什么意思... 是否有任何时间窗口参考? 不出现此问题所需的延迟时间是多少?

谢谢。

Andrea