主题中讨论的其他器件:ALP、 USB2ANY

工具与软件:

尊敬的团队:

我们使用947/948设计了一个新的解决方案、有时屏幕显示屏会抖动、我们转储947/948寄存器映射。

然后我们将它们与正确的模块进行比较、我们发现 NG 模块的948寄存器0x3B = 0x00、正常模块为0x3F。

那么0x3B (EQ 状态)的含义是什么?

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

工具与软件:

尊敬的团队:

我们使用947/948设计了一个新的解决方案、有时屏幕显示屏会抖动、我们转储947/948寄存器映射。

然后我们将它们与正确的模块进行比较、我们发现 NG 模块的948寄存器0x3B = 0x00、正常模块为0x3F。

那么0x3B (EQ 状态)的含义是什么?

您好、Yao、

感谢您发送这些电子邮件。 SER reg 0xA- 0xB 上似乎有一些 CRC 错误、这可能表示 SI 问题。

1.您能否在解串器上探测锁定销,并在闪烁时检查锁定销是否下降

2.反复读取 SER 0xA - 0xB (可能每隔几秒读取一次)、并检查其是否持续增加。

3.如果可能、请按照948数据表中的说明使用 BIST 序列。

并且仅针对您系统上的一些背景:

- SER 和 DES 都在定制电路板上吗?

-测试了多少个单元,有多少显示了这个问题?

-对于 NG 板,问题发生的频率如何?

此致、

Ikram

尊敬的 Ikram:

1.您能否在解串器上探测锁定销,并在闪烁时检查锁定销是否下降

-->>>它仍然是高级别(LOCK);

2.反复读取 SER 0xA - 0xB (可能每隔几秒读取一次)、并检查其是否持续增加。

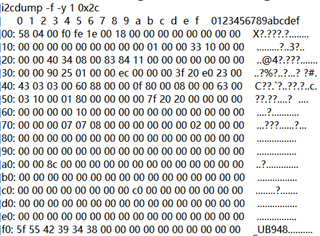

-->>>这次是0xff (参见下面的 pic)、

3.如果可能、请按照948数据表中的说明使用 BIST 序列。

--->>948没有 在我们的主装置上膨胀。

并且仅针对您系统上的一些背景:

- SER 和 DES 都在定制电路板上吗?

-->否

-测试了多少个单元,有多少显示了这个问题?

-->>>我们已经有3个板;

-对于 NG 板,问题发生的频率如何?

-->一个/两个主板:仅1次

第三个板:几乎 0.2~0.5%。

您能解释947的 CRC 寄存器吗:

1:CRC 错误报告越多、连接故障增加、是否正确?

2:如果一个947在每次启动时报告更多的 CRC 错误、表明这个947 是否损坏?

3: 发生振动时、我们可以通过重置947和显示面板(其中948出现凸起)来修复

最好的爬坡。

您好、Yao、

1.反向通道 CRC 错误计数表明存在信号完整性问题。 因此这可能与 IL / RL 在布局、器件选择、连接器、电缆等方面与通道规格不匹配相关

2.所有必要的勘误是否适用于947? 您能否分享该脚本?

3. 锁是否连续探测? 可能只有在抖动/闪烁期间锁定才偶尔下降。

您还可以尝试使用947 SER PatGen 吗? 这将有助于检查是否仅947 LVDS 输入出现闪烁、或者内部 PATGEN 是否也出现闪烁。

此致、

Ikram

您好、Yao、

ALP 是用于测试 FPD-Link 器件的 GUI。 https://www.ti.com/tool/ALP

使用 EVM 进行测试时、您可以从计算机运行 ALP 并通过 USB2ANY 连接到 EVM。

否则、您也可以使用 I2C 适配器(如 Aardvark)将 PC 连接到 FPD-Link 器件的 I2C。

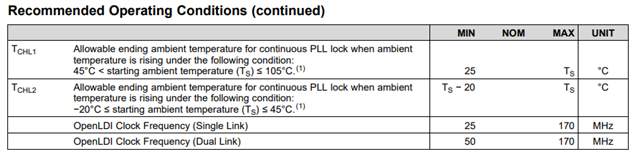

显示时序将针对显示面板。 时序如下所示、或者显示面板数据表可能具有最小值和最大值 平均值

您好、Yao、

您能否检查上电序列是否符合947数据表的要求? 当存在稳定的 OLDI 时钟输入后、PDB 应处于高电平。

此外、您的 PCLK 速率(根据您共享的显示时序)为47.98 MHz。

对于947、该速率(低于50 MHz)仅由仅使用 DOUT0的单链路模式支持。 您是否可以更改 MODE_SEL 设置和电缆连接以便将其置于单链路模式?

此致、

Ikram

尊敬的 Ikram:

非常感谢、我们几乎解决了这个问题、但我们仍有一个问题需要您帮助:

显示面板 在我们的音响主机之前是凸出的、显示面板制定了一条规则、即948初始化和947初始化。

如果显示面板初始化948、请执行以下步骤:

1:显示屏面板 写948寄存器 A;

2:显示屏面板 写 948 寄存器 B;

3:显示屏面板 写 948 寄存器 C;

4:显示屏面板 写 948 寄存器 D;

例 A:如果主机 在步骤2 和步骤3之间写入948寄存器 F、此操作是否会破坏9410的初始化?

案例 B:如果主机 与步骤3同时写入948寄存器 F、此操作是否会破坏9BS 的 初始化?

此致。

您好、Yao、

"Timing Confirmation"代码应在锁定并发送稳定的视频数据后运行。 是否可以更改代码、以便主机 SoC 按顺序执行此代码、而不是在解串器端按 MCU 顺序执行? 有没有方法可以验证在此期间是否发生了显示 I2C 活动?

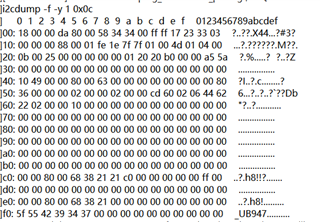

2:我们的任务勘误表3 (下图下)、它们以前只运行过一次、现在我们将它们设置为重试20次;

此外、仅出于测试目的、是否有稳定的视频、或者在运行此完整脚本时、它在运行多次之后是否始终显示错误、如您所述?

此致、

Ikram