Other Parts Discussed in Thread: DP83867E

工具与软件:

嗨、团队:

在数据表8.2.2.2.1 MDI 布局指南中、规定了"MDI 布线必须采用50Ω 接地和100Ω 差分控制阻抗。"

我的客户面临一个问题、即尝试满足100Ω 差分和50Ω 单端要求会导致与仅采用100Ω 差分布线的布局相比、差分信号布线间隔更远。

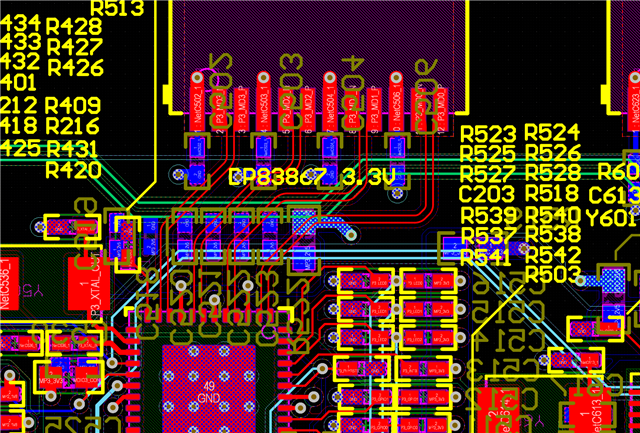

我想以 DP83867E SGMII EVM 的布局图为例展示布局模式。 您能提供这张图吗?

此外、在以下三项要求中是否有优先级存在:100Ω 差分、50Ω 单端和差分信号布线之间的间距?

100Ω 差分和50Ω 单端阻抗的可接受设计容差是多少?

此致、