Thread 中讨论的其他器件:CC3301、 TXS0206A

工具/软件:

你(们)好

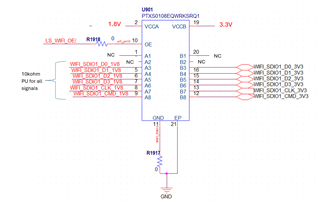

我使用 TXS0108进行 Microchip DSP 3.3V (ATSAMA5D27C-CNR)和 TI WIFI 芯片1.8V (CC3301)之间的 SDIO 通信

在1.8V 侧、对于所有6个 SDIO 信号、我具有一个10k Ω PU 电阻

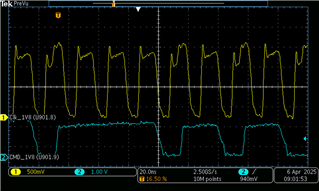

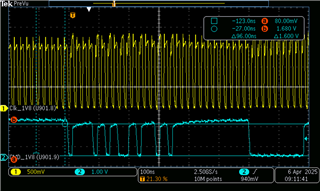

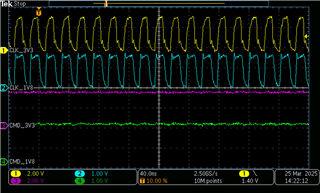

使用示波器对信号进行采样时、我注意到来自 MPU 的3.3V 时钟和 LS 之后的1.8V 时钟运行 正常

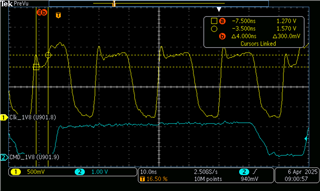

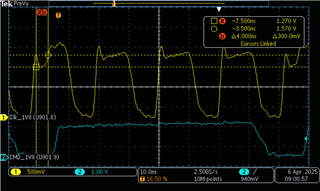

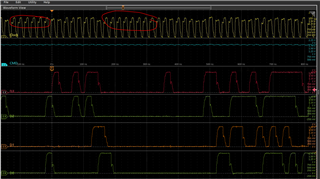

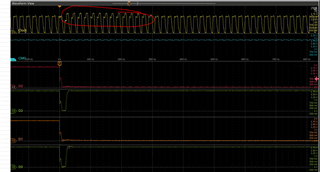

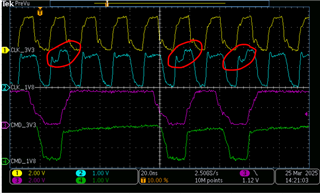

但当我更改其中一个数据或 CMD 信号时、我会在1.8V 时钟侧的时钟上升期间看到压降

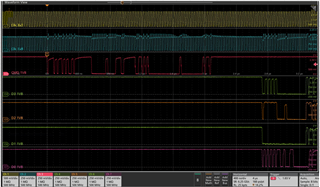

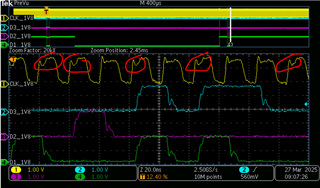

Pic1 -时钟看起来正常、数据或 CMD 不变:

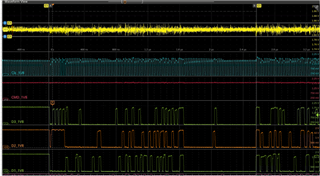

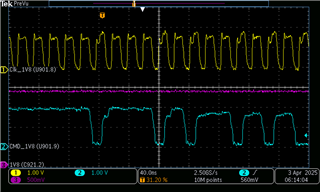

Pic2 -当 CMD 信号发生变化时、1.8V 时钟电压下降

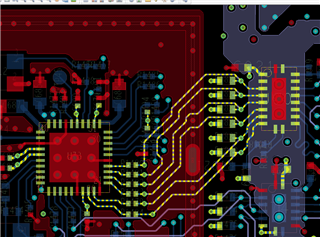

Pic3 - 数据信号发生变化时1.8V 时钟压降

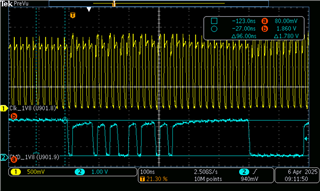

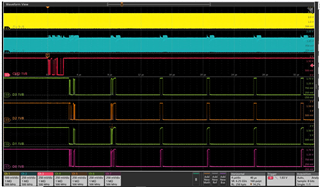

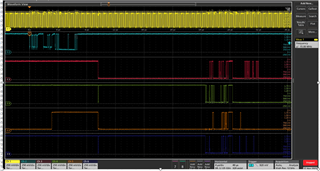

Pic4-我还在 CMD 更改期间测量了1.8V LS 电源并使其保持稳定

请提供建议