您好,

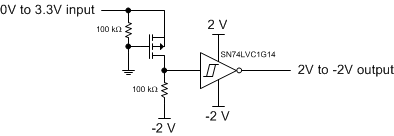

我正在寻找一种电平转换器,它可以将0-3V脉冲输入转换为+2V 至-2V输出 摆动。 此脉冲以~1MHz至100MHz的频率切换。 但我们的工作循环非常小,为1MHz - 100MHz的~2 %。 根据电平转换器的可用性,我们可以选择1MHz-100MHz之间的任何一个频率。 请告诉我是否有任何级别的换档器可用。

此外,请告诉我是否有任何级别转换器接近此规格。

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

您好,

我正在寻找一种电平转换器,它可以将0-3V脉冲输入转换为+2V 至-2V输出 摆动。 此脉冲以~1MHz至100MHz的频率切换。 但我们的工作循环非常小,为1MHz - 100MHz的~2 %。 根据电平转换器的可用性,我们可以选择1MHz-100MHz之间的任何一个频率。 请告诉我是否有任何级别的换档器可用。

此外,请告诉我是否有任何级别转换器接近此规格。

我们计划采用YZP套件。 我们有以下问题:

我们计划采用YZP套件。 我们有以下问题:

1)您建议我们使用哪种NMOS?

2)如果负载盖约为2-3pF,您对此IC (SN74LVC1G14)的功耗有何想法? 在数据表中,它被称为低功率,我只是想知道上述负载盖的编号。

3) YZP和YZV包装有何区别? YZV与YZP相比是否有任何优势,因为只有4个引脚,而不是5个引脚?

让我们知道哪种包装的寄生剂最少。

谢谢!

1)这是PMOS,我不能推荐它,因为TI不制造离散MOSFET,我还远不是离散MOSFET专家。 我建议您选择一种能够支持您的速度要求并具有最小寄生虫的产品。

2)功耗是一个相当复杂的问题。 如果这是您主要关心的问题,我建议您切换到SN74AUP1G14,因为它是专门为最小功耗而设计的。 使用的功率可以使用以下公式计算:

3)这两个软件包基于相同的WCSP技术,非常相似。 我建议使用4引脚YZV,除非您有理由使用5引脚YZP,因为它更节省空间。

您可以在我们的网站上看到IBIS模型中的寄生差异。 我已经为您抓取了相关部分的屏幕截图。