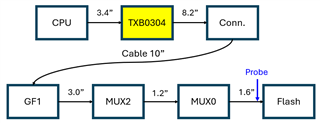

我们使用 TXB0304将33MHz 和16MHz CLK 从1V8传输到3V3。

拓扑 列表如下所示:

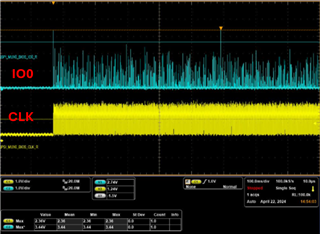

拓扑1:QSPI 16MHz 布线长度在电平位移后为14英寸、 无法识别 CLK 的波形。

是否有任何解决方案可以对拓扑1提供跟踪限制建议? 或者如何评估具有小功能变化的拓扑、

谢谢!

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

高克莱门斯

另外两个问题:

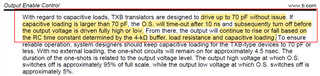

1. TXB 文档指出"如果容性负载大于70pF、O.S 将在10ns 后超时、输出将根据由4-kΩ 缓冲器、负载电阻和容性负载决定的 RC 时间常数持续上升下降。"、 我可以有 介绍振荡的公式或更多详细信息吗? 如何 评估由阻抗不匹配质量或负载过重导致的拓扑?

2.我 想用实际的数字来总结一下 TXB 布线规则

在该文档中、TI 建议控制 总时钟需要小于70pF 且布线长度较短

如果我有新的情况、所有组件 Cload 都约为35pf、但布线长度已经为12"、我认为 Cload 总值可能约为70pf、但如果没有仿真、我们怎么才能判断边际案例将通过

请问您对此有何评论、如果您能提供实际数字规则会更好

谢谢!