工具与软件:

大家好、团队成员:

当我们使用 DRV8702-Q1和 MOSFET 进行测试时、输出电流可能因某种原因被拉低。 请您分享一些对此的见解吗?

我们在电子负载和实际功率电阻方面都发现了该问题。

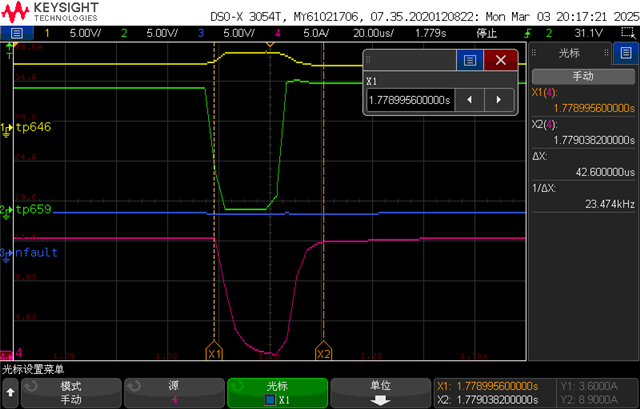

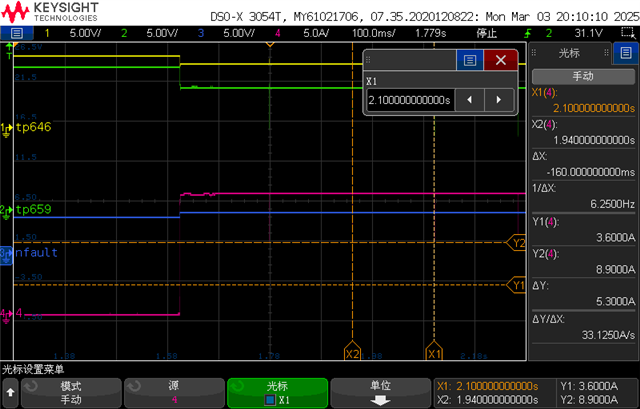

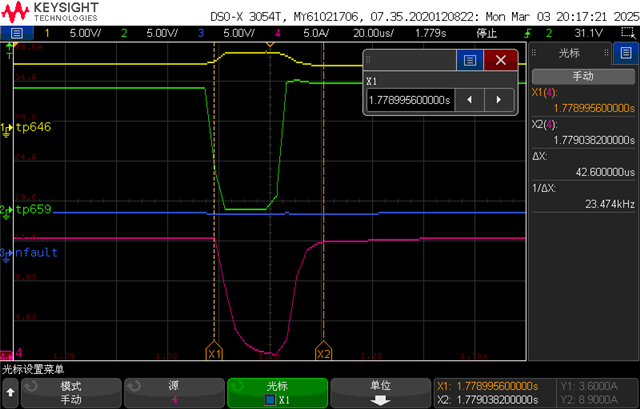

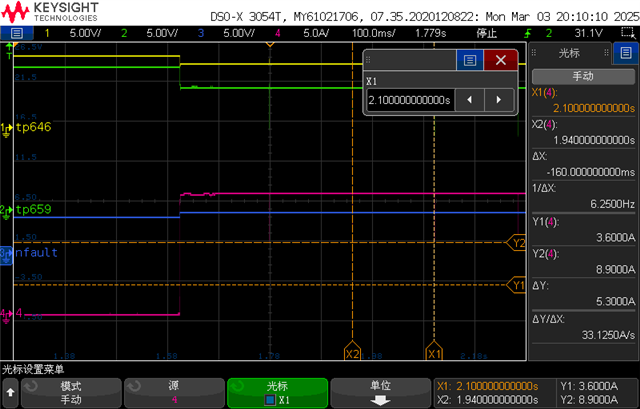

拉低的电流可以保持42us、nFAULT 为高电平、IN 引脚为高电平。 黄色曲线是 MOSFET 栅极波形、蓝色曲线是 nFAULT、粉色曲线是电桥电流。

谢谢

此致!

Frank

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

工具与软件:

大家好、团队成员:

当我们使用 DRV8702-Q1和 MOSFET 进行测试时、输出电流可能因某种原因被拉低。 请您分享一些对此的见解吗?

我们在电子负载和实际功率电阻方面都发现了该问题。

拉低的电流可以保持42us、nFAULT 为高电平、IN 引脚为高电平。 黄色曲线是 MOSFET 栅极波形、蓝色曲线是 nFAULT、粉色曲线是电桥电流。

谢谢

此致!

Frank

您好!

感谢您的提问。 让我在这里尝试挤压一下这个想法。

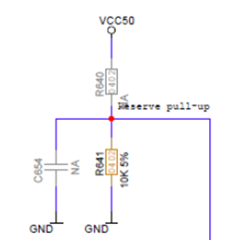

1) MODE 引脚外部电阻。

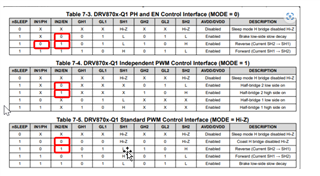

MODE 引脚输入应为0、1或高阻态。 客户的原理图 R641为10千欧、可能会被检测为高阻态。 然后 DRV 处于 PWM 模式。 因此、IN1=0、IN2=1是"反向"-电流可以流动。

如果客户不希望在 IN1=0、IN2=1期间获得电流、则 MODE 引脚通过1k Ω 拉至 DVDD。 那么 DRV 将处于独立模式。

此致

信也

此致

信也