论坛成员、您好!

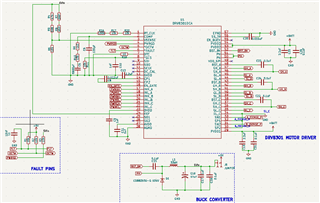

我的电子电路上的 GVDD 引脚一直存在问题、我希望从社区获得一些见解和指导。 当为 GVDD 引脚提供的电压降至5V 以下或升高至15V 以上时、就会出现该问题。 我想在20V - 55V 的范围内运行电路。 我怀疑这种欠压情况可能会导致电路出现某些故障。 我附上了原理图供参考。

观察结果:

降压转换器可在5V 到45V 的范围内正常工作。

布局是根据 TI 指导原则设计的。

以下是我的问题:

-

当电压低于5V 和高于15V 时、GVDD 引脚如何工作? 这些电压范围对电路的性能和可靠性有何潜在影响?

-

GVDD 引脚电压超出指定范围的原因可能是什么? 是否有任何常见的缺陷会导致这个问题?

-

是否有任何建议的电路保护机制或措施可防止出现 GVDD 欠压情况? 如何保护我的电路免受潜在的损坏?

-

是否有任何妥善做法可用于排除 GVDD 欠压事件并确定其根本原因? 我可以使用哪些工具或技术来确定问题?

-

如果有人以前遇到过类似的 GVDD 欠压问题、您能否分享您的经验以及为解决该问题所采取的步骤?

下面附加了一些观察到的波形。

PWRGD

输入脉冲

CP1和 GND 之间

CP2和 GND

EN_GATE 信号

DVDD 信号

AVDD 信号

在5V 至15V 输入电压范围内、GVDD 变为10V。 不过、仍然无法观察到输出脉冲。

在15V 以上时、它变为1.68V 的固定值、FAULT 引脚变为低电平。

我未使用带 SPI 模式的 DRV8301。

我们非常感谢您提供任何帮助或建议。 提前感谢您的支持!