与我现有的源代码一样、SVSLPE 位被清零。

(禁用 SVS 低电平上电复位)

PMMRIE = SVSHPE;

如果 Vcore 下降但没有 POR、会发生什么情况? (例如 MCU 将卡在复位状态)

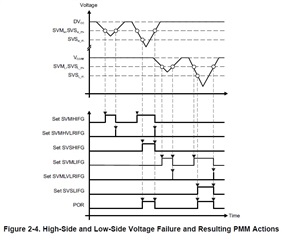

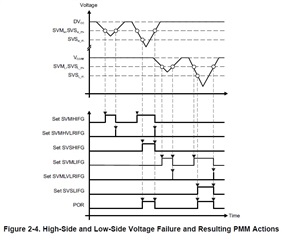

如何仿真 Vcore 压降但保留 DVCC (如用户指南中的图2-4所示)?

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

与我现有的源代码一样、SVSLPE 位被清零。

(禁用 SVS 低电平上电复位)

PMMRIE = SVSHPE;

如果 Vcore 下降但没有 POR、会发生什么情况? (例如 MCU 将卡在复位状态)

如何仿真 Vcore 压降但保留 DVCC (如用户指南中的图2-4所示)?

器件型号:MSP430F6779A

禁用 SVSHPE 和 SVSLPE 的作用是什么?

在没有 POR 的情况下、如果 Vcore 下降、会发生什么情况? (例如、可能发生一些严重事件、例如 MCU 卡滞)

uint16_t PMM_setVCoreUp ( uint8_t level){

uint32_t PMMRIE_backup, SVSMHCTL_backup, SVSMLCTL_backup;

//The code flow for increasing the Vcore has been altered to work around

//the erratum FLASH37.

//Please refer to the Errata sheet to know if a specific device is affected

//DO NOT ALTER THIS FUNCTION

//Open PMM registers for write access

HWREG8(PMM_BASE + OFS_PMMCTL0_H) = 0xA5;

//Disable dedicated Interrupts

//Backup all registers

PMMRIE_backup = HWREG16(PMM_BASE + OFS_PMMRIE);

HWREG16(PMM_BASE + OFS_PMMRIE) &= ~(SVMHVLRPE | SVSHPE | SVMLVLRPE |

SVSLPE | SVMHVLRIE | SVMHIE |

SVSMHDLYIE | SVMLVLRIE | SVMLIE |

SVSMLDLYIE

);

SVSMHCTL_backup = HWREG16(PMM_BASE + OFS_SVSMHCTL);

SVSMLCTL_backup = HWREG16(PMM_BASE + OFS_SVSMLCTL);

//Clear flags

HWREG16(PMM_BASE + OFS_PMMIFG) = 0;

//Set SVM highside to new level and check if a VCore increase is possible

HWREG16(PMM_BASE + OFS_SVSMHCTL) = SVMHE | SVSHE | (SVSMHRRL0 * level);

//Wait until SVM highside is settled

while ((HWREG16(PMM_BASE + OFS_PMMIFG) & SVSMHDLYIFG) == 0) ;

//Clear flag

HWREG16(PMM_BASE + OFS_PMMIFG) &= ~SVSMHDLYIFG;

//Check if a VCore increase is possible

if ((HWREG16(PMM_BASE + OFS_PMMIFG) & SVMHIFG) == SVMHIFG){

//-> Vcc is too low for a Vcore increase

//recover the previous settings

HWREG16(PMM_BASE + OFS_PMMIFG) &= ~SVSMHDLYIFG;

HWREG16(PMM_BASE + OFS_SVSMHCTL) = SVSMHCTL_backup;

//Wait until SVM highside is settled

while ((HWREG16(PMM_BASE + OFS_PMMIFG) & SVSMHDLYIFG) == 0) ;

//Clear all Flags

HWREG16(PMM_BASE +

OFS_PMMIFG) &= ~(SVMHVLRIFG | SVMHIFG | SVSMHDLYIFG |

SVMLVLRIFG | SVMLIFG |

SVSMLDLYIFG

);

//Restore PMM interrupt enable register

HWREG16(PMM_BASE + OFS_PMMRIE) = PMMRIE_backup;

//Lock PMM registers for write access

HWREG8(PMM_BASE + OFS_PMMCTL0_H) = 0x00;

//return: voltage not set

return ( STATUS_FAIL) ;

}

//Set also SVS highside to new level

//Vcc is high enough for a Vcore increase

HWREG16(PMM_BASE + OFS_SVSMHCTL) |= (SVSHRVL0 * level);

//Wait until SVM highside is settled

while ((HWREG16(PMM_BASE + OFS_PMMIFG) & SVSMHDLYIFG) == 0) ;

//Clear flag

HWREG16(PMM_BASE + OFS_PMMIFG) &= ~SVSMHDLYIFG;

//Set VCore to new level

HWREG8(PMM_BASE + OFS_PMMCTL0_L) = PMMCOREV0 * level;

//Set SVM, SVS low side to new level

HWREG16(PMM_BASE + OFS_SVSMLCTL) = SVMLE | (SVSMLRRL0 * level) |

SVSLE | (SVSLRVL0 * level);

//Wait until SVM, SVS low side is settled

while ((HWREG16(PMM_BASE + OFS_PMMIFG) & SVSMLDLYIFG) == 0) ;

//Clear flag

HWREG16(PMM_BASE + OFS_PMMIFG) &= ~SVSMLDLYIFG;

//SVS, SVM core and high side are now set to protect for the new core level

//Restore Low side settings

//Clear all other bits _except_ level settings

HWREG16(PMM_BASE + OFS_SVSMLCTL) &= (SVSLRVL0 + SVSLRVL1 + SVSMLRRL0 +

SVSMLRRL1 + SVSMLRRL2

);

//Clear level settings in the backup register,keep all other bits

SVSMLCTL_backup &=

~(SVSLRVL0 + SVSLRVL1 + SVSMLRRL0 + SVSMLRRL1 + SVSMLRRL2);

//Restore low-side SVS monitor settings

HWREG16(PMM_BASE + OFS_SVSMLCTL) |= SVSMLCTL_backup;

//Restore High side settings

//Clear all other bits except level settings

HWREG16(PMM_BASE + OFS_SVSMHCTL) &= (SVSHRVL0 + SVSHRVL1 +

SVSMHRRL0 + SVSMHRRL1 +

SVSMHRRL2

);

//Clear level settings in the backup register,keep all other bits

SVSMHCTL_backup &=

~(SVSHRVL0 + SVSHRVL1 + SVSMHRRL0 + SVSMHRRL1 + SVSMHRRL2);

//Restore backup

HWREG16(PMM_BASE + OFS_SVSMHCTL) |= SVSMHCTL_backup;

//Wait until high side, low side settled

while (((HWREG16(PMM_BASE + OFS_PMMIFG) & SVSMLDLYIFG) == 0) ||

((HWREG16(PMM_BASE + OFS_PMMIFG) & SVSMHDLYIFG) == 0)) ;

//Clear all Flags

HWREG16(PMM_BASE + OFS_PMMIFG) &= ~(SVMHVLRIFG | SVMHIFG | SVSMHDLYIFG |

SVMLVLRIFG | SVMLIFG | SVSMLDLYIFG

);

//Restore PMM interrupt enable register

HWREG16(PMM_BASE + OFS_PMMRIE) = PMMRIE_backup;

//Lock PMM registers for write access

HWREG8(PMM_BASE + OFS_PMMCTL0_H) = 0x00;

return ( STATUS_SUCCESS) ;

}尊敬的 Tink:

为了防止在 VCORE 设置期间发生意外的 POR、SVSHPE 和 SVSLPE 被禁用。 如果您的 VDD 降至所需的运行水平以下、您仍将获得 POR。

VCORE 的破坏性条件可能是 布线过于接近 VCORE 引脚/ VCORE 电容器的寄生效应。 由于 PCB 设计而耦合到 VCORE 上的其他信号可能会导致 VCORE 波动并将电压降至预期值以下。 一般来说、如果让其他信号布线远离 VCORE、寄生效应是不存在问题的;VCORE 引脚是一个转角引脚、因此可更轻松地使 VCORE 远离其他信号。

我已经注意到了几个帖子、其中涉及 VCORE 电平增加的操作以及 MCU 卡滞事件的可能性。

此致、

卢克

1) 1)您是否在运行期间仔细研究了 VCORE 电容器以查看 MCU 卡滞时的值?

是的、我已经测量了 MCU 卡住时的 VCORE、(VCORE)= 1.42V

2) 2)您如何识别 MCU 的代码进度?

通过以下证据进行检查

1) 1)复位引脚变为高电平:如果代码过程中、复位引脚因 NMI 功能而应变为低电平。

2) Vcore:如果代码处理 Vcore 应更改为2、3、0 LPM 及我们的功能

但这次只停留在 VCORE 0 (1.42V)

它是否会在代码中一致的行停止?

我发现、只有代码在系统预初始化函数处停止、但在实验练习中却不能使其停止。

int system_pre_init(void)

{

WDTCTL = WDTPW+WDTHOLD;

// Clear RTCHOLD Bit after reset

RTCCTL0_H = RTCKEY_H; // unlock

RTCCTL1 &= ~RTCHOLD; // release RTC

RTCCTL0_H = 0x00; // lock

SFRRPCR = SYSNMI | SYSNMIIES | SYSRSTRE;

return 1;

}

3) 3)您是否能够轻松复制您正在运行的问题以运行其他测试、还是看起来是随机的?

我无法在实验室中重现此问题、只能在实际使用现场找到。

Luke、您好!

另外在2上、您是否能够连接到器件并单步执行代码?

否、我没有使用调试器来检查实际样本" MCU 变回卡滞"。 因为我担心它会复位 MCU 或程序计数器(因此、问题和原因证据可能消失)。

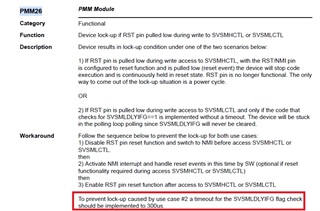

好的、我已经使用 PMM26使用另一个板(修改后的源代码)重现了情况、从而使"MCU 停止运行"。

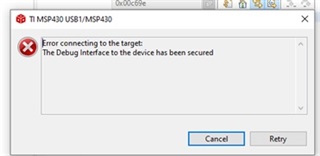

尝试使用调试器后 、无法使用 CCS 连接到 MCU。

您是否在多个器件上看到过这种情况?

是的、实际应用中的多个器件中会出现问题(我估计为0.5到1 %)。

您是否检查了 PMM 错误 以验证工艺流程中是否未运行任何此类方案?

是的、我已经查看了勘误表。 源代码主要用作预防权变措施过程。

除了我在下面发现的一点。

"为了防止用例2引起的锁定、SVSMLDLYIFG 标志检查的超时

应该实施到300us。"

但我不认为以上内容会导致这个问题、因为在源代码中没有拉取检查。 SVSMLDLYIFG== 1.

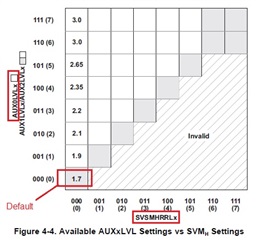

我怀疑另外一点、为什么 AUX0LVL 和 SVSMHRRL 的默认值位于用户指南中的无效区域(AUX0LVL = 0、SVSMHRR = 0)。

这可能会导致 MCU 像我发现的那样卡在复位状态中运行?

多个[/报价]

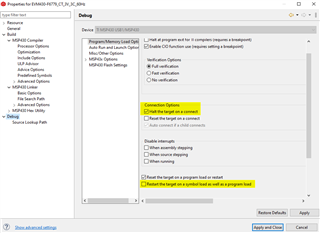

我未在该线程中看到将 RST 引脚设置为 NMI 中断而不是 RST 函数的代码片段。 您是否认为这是现场可能出现的情况? 您的器件在哪里设置了 SVS 模块并且发生了一个 rst? 最好在 PMM SET VCORE 功能之前添加此特性、以将 RST 引脚更改为 NMI。

在 NMI 中、您仍然可以如何处理您认为合适的中断(是实际重置代码还是继续进行 VCORE 设置)。

对于 CCS 连接、在工程属性中、您可以将调试器设置为"连接时暂停"、而不是连接时复位。 您还可以加载代码中的符号、以便 CCS 和调试器可以连接和单步执行、而无需对器件进行复位或编程。

——

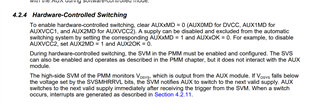

AUX0LVL 问题。 这仅适用于启用开关的情况、默认情况下禁用开关。

我建议您在启用切换时增加 AUX0LVL 的电平。

此致、

卢克

尊敬的Luke Ledbetter:

关于在您启用切换时增大 AUX0LVL 的电平。

您认为下面的代码是正确的吗? 这是关于设置电平、然后解锁要切换的电源。

如果在第一行变为 AUXKEY (同时解锁)、过程是否正确?

AUXCTL0_H = AUXKEY_H;

AUXIE = 0x0000; // AUXIE

AUXCTL2 = (AUXMR_0 | AUX0LVL_6 | AUX1LVL_3 | AUX2LVL_0);

AUXIFG &= ~(AUX0SWIFG | AUX1SWIFG | AUX2SWIFG | AUX0DRPIFG | AUX1DRPIFG | AUX2DRPIFG | AUXMONIFG | AUXSWNMIFG);

AUXCTL1 |= AUX2MD; // AUXCTL1 Software controlled AUXVCC2 auxiliary supply mode.

AUXCTL1 &= ~(AUX0MD | AUX1MD); // Hardware controlled AUXVCC1 auxiliary supply mode.

// Hardware controlled AUXVCC0 auxiliary supply mode.

AUXIFG &= ~(AUX0SWIFG | AUX1SWIFG | AUX2SWIFG | AUX0DRPIFG | AUX1DRPIFG | AUX2DRPIFG | AUXMONIFG | AUXSWNMIFG);

// AUXIFG

if ((AUXCTL0_L & LOCKAUX_L) == LOCKAUX_L) // Auxiliary is locked because of core power down?

{

AUXCTL0_L &= ~LOCKAUX_L; // Release Auxiliary module from core power down

}

Luke、您好!

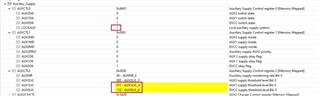

让我们返回、预置我的源代码。

步骤1:在行1之前 AUXCTL0_H = AUXKEY_H;

第2步:在行1 AUXCTL0_H = AUXKEY_H 之后;

步骤3:在行3之后 AUXCTL2 = (AUXMR_0 | AUX0LVL_6 | AUX1LVL_3 | AUX2LVL_0);

第4步:在行13 AUXCTL0_L &&~LOCKAUX _L 之后;

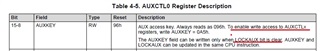

为什么这个代码可以在没有"写入 AUXKEY 和 LOCKAUX 位被清零"的情况下写入步骤3中的设置(步骤1只写入密钥)?

它是否与用户指南相冲突?