Other Parts Discussed in Thread: TRF7960A, TRF7970A, TRF7960

主题中讨论的其他器件: TRF7970A、 TRF7960

大家好、

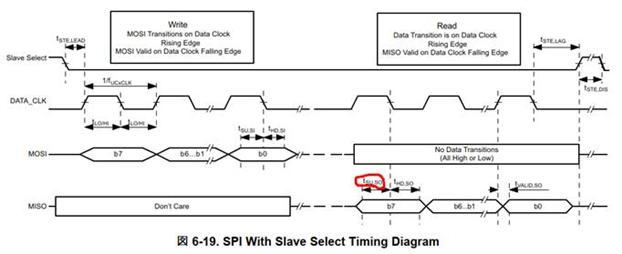

TRF7960A 的数据表指出、Tsu、SO 从 MISO 变化变为 DCLK 上升、如下所示。 这是误导性下降沿吗? 第一个位也很短。

TRF7970A 的数据表指定了一个下降边沿。

< TRF7960A 的数据表:SLOS732G >

< TRF7970A 的数据表:SLOS743M >

谢谢、此致、

Kuerbis