工具与软件:

你(们)好、

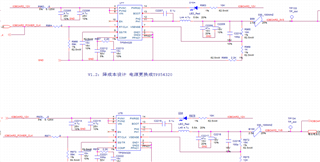

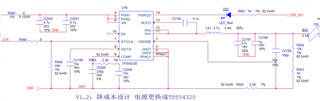

我们有3个板载 TPS54320。 如下面所示。 FPGA IO 提供外部时钟来驱动两个三电源 IC。 800kHz

开始时、FPGA 输出 外部时钟作为高电平信号、我们希望 IC 由 RT 电阻器工作。 不过、此时 PH 波形约为60kHz、输出纹波大至1Vpp。 这是异常的。

然后 FPGA 输出800kHz 50%占空比外部时钟、50ms 后、PH 波形正常800kHz。

奇怪的是、当不同电路板上的温度为-20°C 时、这种问题偶尔会出现。 我们可通过在 TPS54320上使用冷冻喷雾器来重复这种现象。

我们注意到、3个 RT 电阻器实际上是并联的、因此等效 RT 电阻器为59K/3。 但我们无法理解60kHz PH 是如何产生的。 问题:

1、您可以提供三个 IC 内部的 RT/CLK 引脚的内部结构吗?

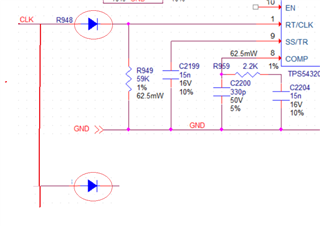

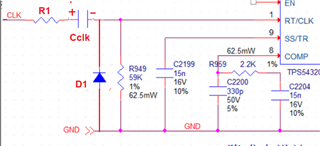

2、我们尝试将外部时钟(R948等)上 的0欧姆更改为电容器、当交流耦合时、情况变得正常。 我们不想插入3个独立的缓冲器(PCB 版本)、 我们可以像这样使用吗 ? 数据表中无相关信息。

欢迎提出任何其他建议、尤其是关于低温的建议。