工具/软件:

您好、

我将使用 LM5143生成单路输出(10Vin 至3.3V @ 30A)。 这个降压控制器是否可用于单输出? 如果是、您能否分享任何参考信息。

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

你好、Roshan

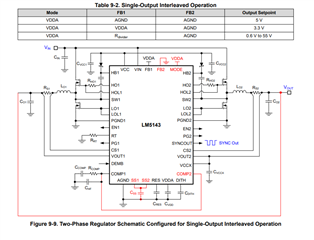

是的、它可用于单路输出。 检查以下配置

我建议您使用 LM5143DESIGN-CALC 计算工具|德州仪器 TI.com 进行设计计算。 这是一个非常有用的工具。 此外、检查此参考设计- PMP23262参考设计| 德州仪器 TI.com

谢谢你

此致

Onkar Bhakare

您好、Onkar Bhakare、

感谢您的答复。 我设计并生产了具有单通道配置的模块、并使未使用的引脚保持开路、EN2连接到 AGND。 电路工作正常。 我的配置 FB1-Buck VDDA。 开关频率:400kHz。 降压电感器:1uH (IHLP6767GZER1R0M01)。 电流检测类型:电感器 DCR (RCS-7.5K、CCS0.2uF)、输出电容:1.8mF、软启动上升时间:2.3ms

但在启动过程中、降压高 FET 导通达10us。 IC 工作序列也是底部 FET 导通后第一个导通的顶部 FET。 另外、在 OUT 开关时、自举电容器会充电至3.5V (有关电路参考、请参阅数据表电路)。 因此、当高 FET 的第一个脉冲导通时、输出电压变为2V。 我在输入电压为9V 时启用转换器。 我的降压转换器输出电压与软启动上升时间不匹配。 您能介绍一下 LM5143的开关顺序吗

谢谢、此致

Roshan

您好、Onkar Bhakare、

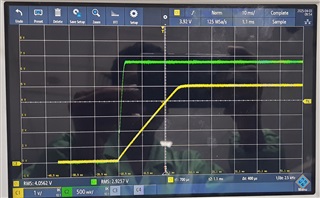

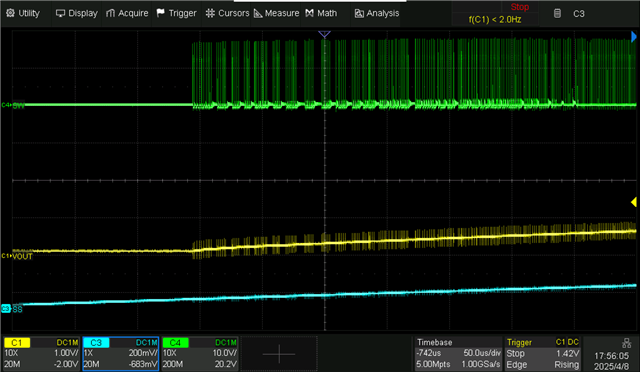

很抱歉、延迟回复、请参阅测试波形表。 并提供您的反馈

CH1:+10Vin 开关

Ch2:底部 FET 栅极

Ch1:3.3V 输出电压

CH2:+10Vin SW

CH1:3.3Vout (放大启动)

CH2:+10Vin SW (放大的第一个脉冲)

CH1:软启动引脚

CH2:3.3V 输出电压

CH1:软启动引脚(放大启动)

CH2:3.3Vout (放大启动)

您好、Roshan

SS 具有内置失调电压;一旦超过内部阈值电平、器件就会跟随 SS。

您共享的波形有两部分

在启动时、补偿电压超过其基准并且器件开始开关、但基准电压仍为0V、因此器件停止开关、可以看到输出电压逐渐下降、由于器件在空载条件下运行、其最小值。 SS 超过内部阈值后、输出将在 SS 之后开始、总启动时间非常接近设计值

希望这些都能回答您的问题。 如果需要进一步的帮助、请告诉我

谢谢你

此致

Onkar Bhakare

您好、Onkar Bhakare、

感谢您的答复。 在我看来、反馈基准将以软启动电压为基准升高。 因此、如果 ss 电压为0V。 FB 基准将为0V。 因此、COMP 电压也为0V。 我也有另一个疑问。 我的开关频率为400kHz。 所以我的总时长是2.5us。 但控制器第一个脉冲导通时间接近12 μ s。 我不知道为什么控制器允许 Ton 时间周期超过其固定时间周期。 我将 DEMB 引脚连接到 VDDA、因此转换器在 FPWM 模式下运行。

谢谢、此致

Roshan

你好、Roshan

[引述 userid="648728" url="~/support/power-management-group/power-management/f/power-management-forum/1495331/lm5143-to-configure-lm5143-as-single-output/5753759 #5753759"]反馈基准将以软启动电压为基准提高。 因此、如果 ss 电压为0V。 FB 基准将为0V。 因此、补偿电压也为0V。[/报价]-是的,这是正确的,但它会在 SS 超过内部阈值电压后成立

另外、我还有一个疑问。 我的开关频率为400kHz。 所以我的总时长是2.5us。 但控制器第一个脉冲导通时间接近12 μ s。 我不知道为什么控制器允许 Ton 时间周期超过其固定时间周期。 我将 DEMB 引脚连接到 VDDA、因此我的转换器以 FPWM 模式运行。[/报价]如果您查看 启动期间的过零阈值、这与 VDEMB = 0V (PFM 情况)类似。 过零是 PFM 逻辑的一部分。

因此、您会在启动期间看到 PFM 行为

谢谢你

此致

Onkar Bhakare

您好、Onkar Bhakare、

感谢您的答复、

后会为真是的、这是正确的、但在 SS 越过内部阈值电压

我还怀疑、如果在 SS 超过内部阈值后反馈基准跟随 SS、则反馈基准将如何相对于 SS 升高时间保持平滑。 此外、在数据表测试波形中、输出没有阶跃升高。

如果您查看 启动期间的过零阈值、它类似于 VDEMB = 0V、PFM 情况。 过零是 FPWM/QUOTE PFM 逻辑的一部分。

因此、您在启动期间看到 PFM 行为

可以、但在数据表中他们没有提及任何巨大的 PFM 范围。 如果控制器将按此顺序运行、则如何以软启动电压为基准提高输出。

谢谢你

此致

Onkar Bhakare

你好、Roshan

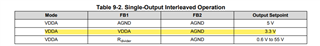

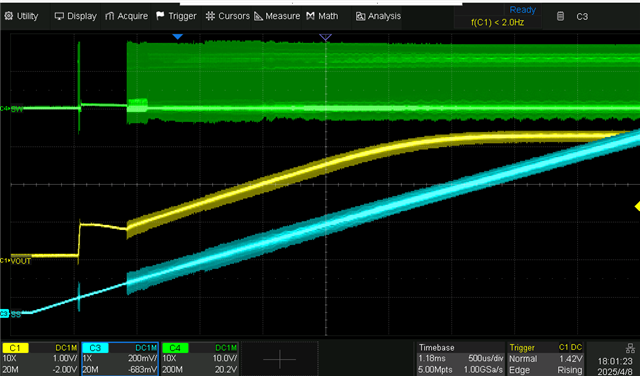

我测试了 EVM 上的单路输出配置。 我没有注意到输出电压有任何大跳变

此外、您可以在启动期间看到 PFM 操作了几个周期

请您确认电路中 MODE 引脚的状态

我尝试使用 MODE = VDDA (单输出交错运行)、以下波形显示了此配置下的行为

如果只想使用单通道、应将 MODE 连接到 AGND。 很抱歉、我在推荐中错过了这一点。

希望这能回答您的问题

谢谢你

此致

Onkar Bhakare

你好、Roshan

我在上次的答复中已经说过。 在 SS 超过内部失调电压之前、器件不会获取 SS 基准。 基准将为零。 Vout 略有变化会导致 COMP 变为高电平、因此 Vout 将立即上升。 由于采用内部设计、这在多相设置(MODE = VDDA)中更为突出。 COMP 将尝试校正该值、但由于环路延迟会增加到显著值。 由于负载电流为零、输出不会放电太多、并将保持接近增加值。

此致

Onkar Bhakare

您好、Onkar Bhakare、

感谢您的答复、

我已经在我的前一个答复中谈到了它。 在 SS 超过内部失调电压之前、器件不会获取 SS 基准。 基准将为零。 Vout 略有变化会导致 COMP 变为高电平、因此 Vout 将立即上升。 由于采用内部设计、这在多相设置(MODE = VDDA)中更为突出。 COMP 将尝试校正该值、但由于环路延迟会增加到显著值。 由于负载电流为零、输出不会放电太多、并且将保持接近增加的值。

如果我们将转换器配置为交错、则转换器输出将随着 ss 的升高而平滑升高、或者作为步骤升高。

谢谢、此致

Roshan

您好、Onkar Bhakare、

感谢您的响应、我有另一个模块是交错配置(50vin、5V@30A)。 其输出跟随相对于 SS 电压的变化。

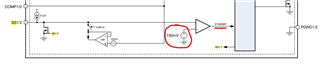

但是、当我们将单通道用作(MODE = VDDA)时、 通过将 EN2连接到 GND 并将 VCCX 连接到 GND、将 FB2连接到 VDDA、即可将 CH2未使用引脚保持开路状态。 在输出端观察到阶跃升高。 同样、在将 FB2与外部反馈电阻器采用相同配置的情况下、可以观察到输出升高情况(与电压升高相关)。

谢谢、此致

Roshan

你好、Roshan

同样、在将 FB2相同配置到外部反馈电阻器的情况下、观察到输出升高与 SS 电压升高相关。

感谢您告知我们您的观察结果。 我以前没有试过

此致

Onkar Bhakare

您好、Onkar Bhakare、

感谢您的答复、

感谢您让我们了解您的观察结果。 我以前没有尝试过

请告诉原因

谢谢、此致

Roshan