工具/软件:

您好:

我们在 SEPIC 模式下对您的元件实施了一个稳压器、可产生110V 的输出、并具有16.8V 至137.5V 的宽输入范围

原子 正在工作、但由于 LM51561H 行为及其电路、EMI 干扰非常高。 我们需要把最低的比率调低至15-20dB、以符合铁路的标准。

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

你好 Silvana,

感谢您分享示波器图。

当我在 SW 节点的上升沿和下降沿都看到振铃时、您能测量 SW 节点的振铃频率吗?

您能否证实 SW 节点的振铃频率与未通过 EMI 测试的频率相同?

如果是、我建议通过在 FET 的栅极信号处添加栅极电阻或在 SW 与地之间添加缓冲电路来优化 FET 的速度。

此外、我建议添加100 Ω R5电阻。 它有助于滤除电流检测信号中的高频噪声。

此致、

Hassan

您好 Hassan、

遗憾的是、干扰位于很宽的频段。 24V 电源电压、水平30MHz 频率为1GHz 时的结果如下:

我们实际上已经尝试添加栅极电阻:为了符合标准,我们必须使用100R,但我们注意到电路中有一些发热。

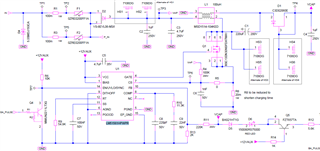

我们还将 R5更改为4K7、并在下面的原理图中更改了所有红色元件。

使用修改后的电路、 我们只能将 EMI 降低到24V、但无法将其解决至110V 电源、这是我们的上限。

你好 Silvana,

感谢您分享 EMI 结果。

根据结果可以清楚地看到导致问题的频率频谱。

首先、我不建议使用超过10 Ω 的栅极电阻、因为这会导致更多的开关损耗。 我建议为低侧 FET 添加并联栅源电容以降低开关速度。

此外、您的设计中是否使用屏蔽式电感器?

此外、PCB 寄生效应也会导致该 EMI 问题。 因为快速 di/dt 会导致电源环路寄生电感上出现高电压尖峰、进而导致 EMI。

您能分享布局文件吗?

此致、

Hassan

你好 Silvana,

是的、我建议使用4层 PCB。 并使用顶部焊盘底层进行电源布线。 尝试将电流路径放置在电流返回路径顶部。 这样、电源环路寄生电感将会因为磁场消除而尽可能地减小。

尝试在电源环路的顶层添加接地平面、这也会消除磁场。

使用第三层和第四层进行信号路由。 第三层为模拟接地、底层为信号。

是的、您尚未在输入和输出端使用去耦电容器。 尝试 在输入和输出端(100nF)添加多个去耦电容器。

尝试减小栅极环路面积、因为这也会成为 EMI 的来源。 尝试与栅极建立较短的连接。 如果对栅极信号使用这两层、栅极信号的传入和返回路径应彼此靠近或相互重叠。

除此之外、请在 SW 节点处添加缓冲电路。 尝试使用 Power Stage Designer 计算 Sepic 的 RC 缓冲器网络值。

通过一根连接线将 PGND 与 AGND 连接起来。

是的、如果它不是电池驱动器件、则可以添加滤波器将 GND 连接到 EARTH。 还会为器件提供 ESD 保护。

此致、

Hassan