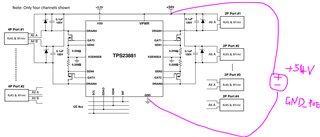

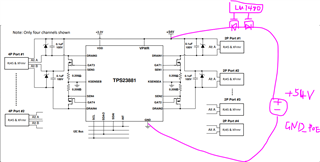

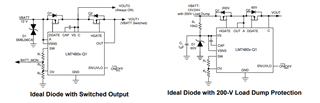

Other Parts Discussed in Thread: TPS23881, TS3A5018, TPS1101, LM7480

主题中讨论的其他器件:TS3A5018、TPS23881、 CSD18536KCS、 LM7480

工具/软件:

尊敬的 Sirs:

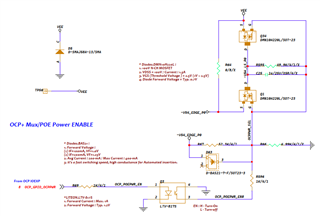

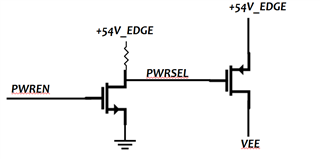

电流,我有一个电源使能控制设计要求作为列表,之后会选择 TI pmos & nmos 组合解决方案;但是,不确定这个想法是否好?!

项目源将提供"-54V (负电压)"电源轨和开关状态(平均切断)的可能设置关闭状态、然后具有外部信号来控制启用开启/关闭、

下面是我的设计示例:

[注:+54V_EDGE 等于-54V (负)电源轨]

BRS

作者:Neil Chen