请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

器件型号:TPS23734 工具/软件:

尊敬的团队:

我们在设计中使用了 TPS2373-4RGW PoE PD 控制器。 硬件已组装、目前正在测试中。

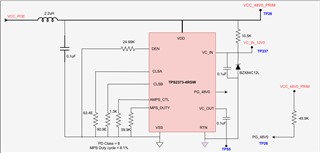

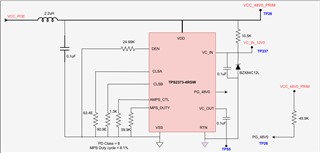

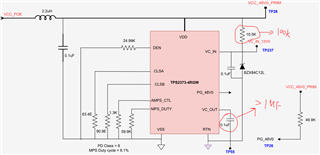

附加了 TPS2373-4RGW 设计部分的图像。

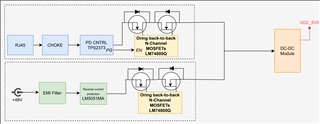

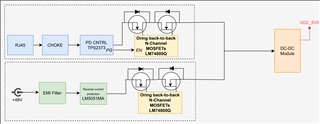

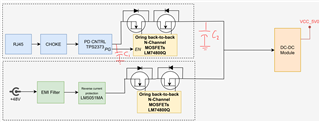

电源部分的方框图。

观察结果:

请告知我们这些事件的潜在原因。

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

工具/软件:

| 探测点 | 正极探头 | 负极探针 | 预期电压 | 测量电压 |

| VCC_48V0_PRIM | TP26 | TP55 | 53-57VDC | 53.65V |

| VC_IN_12V0 | TP237. | TP55 | ~12V | 12.09V |

| PD 控制器 PG_48V0 | TP36 | TP55 | ~9V | 0.3V |

尊敬的 Lenin:

感谢您的联系

有两件事可能相关:

1.VC_OUT 需要比 VC_IN 高10倍。 还建议在该电阻器上使用100k 而不是10.5k 电阻器、以降低功率损耗

2. VDD - RTN 之间的 C1通常需要比 C2大10到20倍。 因此、当背对背断路器导通 C1时、有助于为 C2充电、而不会使 C1上出现过大的压降。

否则、C2充电可能会导致过高的浪涌和 TPS2373-4折返。

此致、

DIAN