工具/软件:

您好:

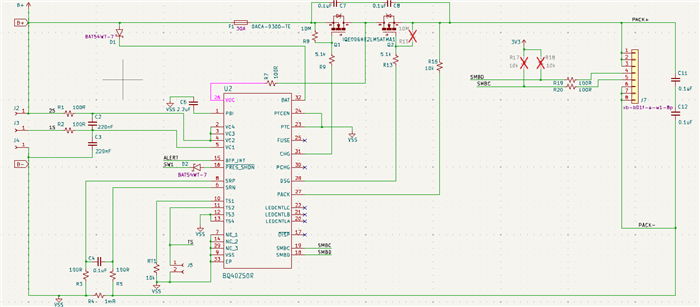

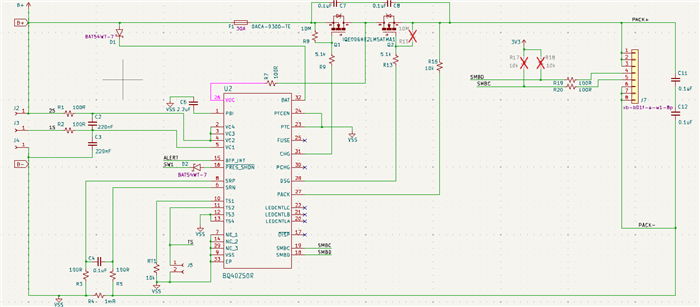

在我的设计(见下文)中启用 DSG 和 CHG FET 时遇到问题、我认为寄存器设置正确、我已针对2节电池包进行了设置、这已清除了任何 CUV 故障。 据我所知、没有可见的故障。

当 PRES 引脚被拉至低电平(已连接)时、我确实会在 CHG FET 栅极上看到脉冲。

希望我错过了一些明显的信息、您可以向我指出正确的方向。

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

工具/软件:

您好:

在我的设计(见下文)中启用 DSG 和 CHG FET 时遇到问题、我认为寄存器设置正确、我已针对2节电池包进行了设置、这已清除了任何 CUV 故障。 据我所知、没有可见的故障。

当 PRES 引脚被拉至低电平(已连接)时、我确实会在 CHG FET 栅极上看到脉冲。

希望我错过了一些明显的信息、您可以向我指出正确的方向。

您好、Michael、

检查完您的原理图后、您的原理图似乎操作正确、我在下面只有一条建议、但这应该与您的当前问题无关。 出于调试目的、我会使用"Command"选项卡并切换 CHD 和 DSG FET、以确保其正常工作。 但是、您的问题很可能与您设置 DSG/CHG Current Threshold 的方式有关。

原理图建议:

-在100欧姆电阻器上串联一个200欧姆电阻器以提高信号质量,并将二极管接地以防止 ESD 损坏

谢谢您、

Alan