工具/软件:

大家好!

我们目前正在使用 LM5050进行一项设计。

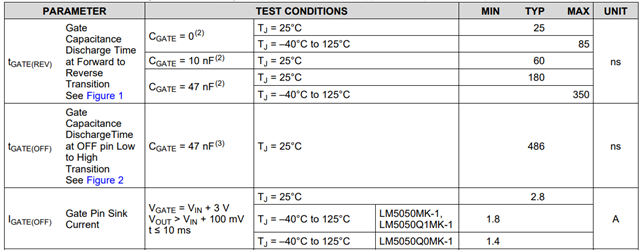

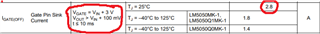

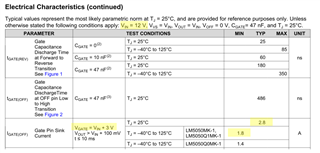

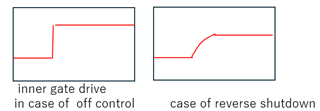

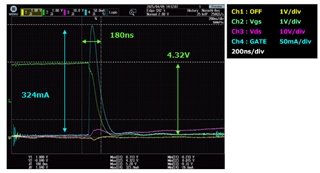

关于从正向转换到反向、以及 OFF 引脚从低电平转换为高电平时的栅极关断时序、

您能否告诉我在以下条件下测得的 tGATE (REV)和 tGATE (OFF)的最大值?

[测量条件]

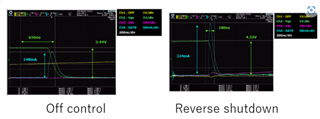

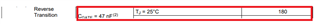

・tGATE (REV)

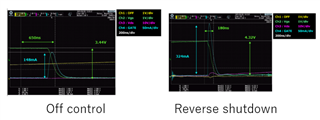

25℃

VGS:4.32V

Δ t tGATE (・)

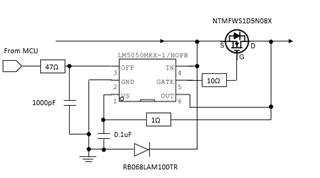

25℃

VGS:3.44V

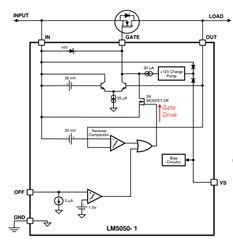

作为参考、我们附加了电路图和我们测量的波形。

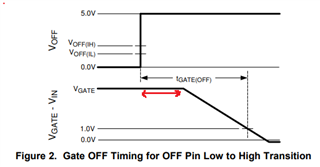

电路图

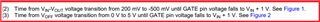

OFF 引脚低电平到高电平转换的栅极关断时序

正向至反向转换的 GATE 关断时序

如果有任何类似的例子、请提供一个链接。

此致、

Tamaki