工具/软件:

您好、团队、

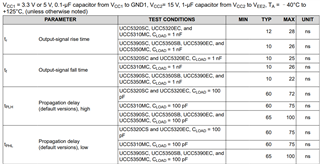

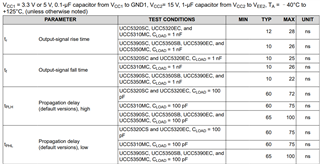

在使用 UCC5350MCD_TRANS-PSpiceFiles 文件后、我们希望评估 UCC5350MCDR 器件时序、以便在100pf 负载下重现数据表中的性能(例如 TR 10ns、tPLH = 65ns~100ns)。 如果有效、我们将添加自定义电路以获得实际结果。 但 PSpice 仿真结果似乎不同,您能帮助检查我们如何在这里获得目标结果吗?

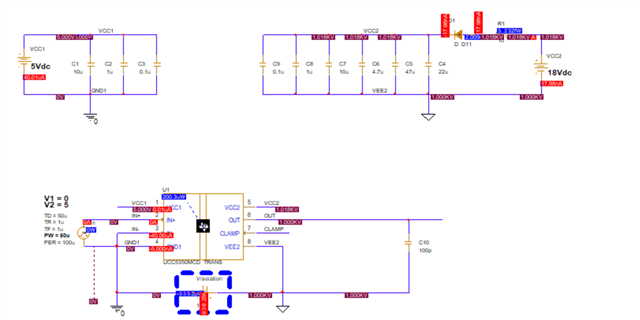

我们现在设置:

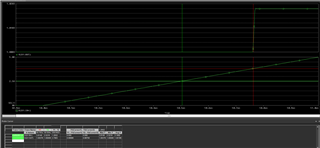

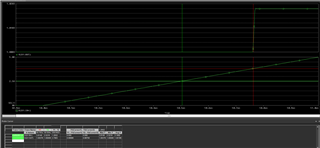

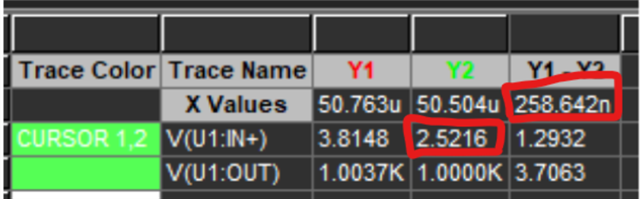

结果: tPLH 输出为260ns

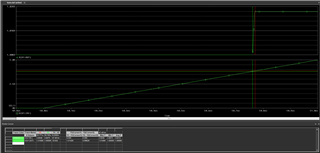

tr 为9.25ns 正确。

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

工具/软件:

您好、团队、

在使用 UCC5350MCD_TRANS-PSpiceFiles 文件后、我们希望评估 UCC5350MCDR 器件时序、以便在100pf 负载下重现数据表中的性能(例如 TR 10ns、tPLH = 65ns~100ns)。 如果有效、我们将添加自定义电路以获得实际结果。 但 PSpice 仿真结果似乎不同,您能帮助检查我们如何在这里获得目标结果吗?

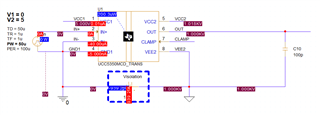

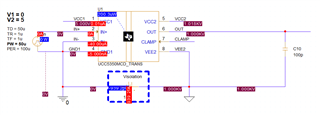

我们现在设置:

结果: tPLH 输出为260ns

tr 为9.25ns 正确。

您好 Allen、

您能否共享 PSPICE 仿真文件? 我将进一步调查。 UCC5350的 tp_lh 传播延迟为55ns、tp_hl 约为54ns。 100ns 的宽最大容差基于工艺角和温度。

这是一个非常慢的输入上升时间。 在输入超过输入阈值之前、我们的传播延迟不会开始。 在这种情况下、应从 IN+为0.55 x 5V 或2.75V 时开始测量传播延迟。 从该阈值测得的值是否为260ns?

此致、

Sean

您好 Sean、

我正在使用 TI.com 下载的 sllm368a.zip 文件。

我 按如下所示删除输出电路、并按数据表中所述的方式删除 tp_lh 传播延迟目标。

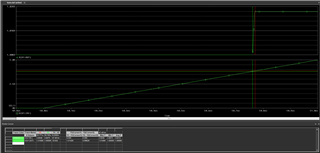

是的、我测量了0.5 * Vin +至10%* Vout、因此我们可以在此处看到一致性详细信息:

您好 Allen、

开始时的脉冲由串联电感引起。 它向栅极驱动器的输出提供瞬态高阻抗。

我在第一个 TPLH 图中设置了50ns/div。 用于此测量的示波器是在2.5V 的输入端触发的、因为输入是5V 方波。

您可以看到、输出在大约50ns 时开始上升。但是、它会在不同的时间达到9V 中点到18V 电源、具体取决于栅极驱动器的驱动强度。

总之、虽然 Cload 会影响栅极驱动器的上升时间、但它不会延迟输出在接收到输入信号后开始上升所需的时间。

此致、

Sean