工具/软件:

尊敬的团队:

请查看下面随附的布局(还随附了原理图)、并提供 Vin - 12V、Vout - 5V 的反馈。

/cfs-file/__key/communityserver-discussions-components-files/196/TPS56628DDA_5F00_5V.brd

谢谢

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

工具/软件:

尊敬的团队:

请查看下面随附的布局(还随附了原理图)、并提供 Vin - 12V、Vout - 5V 的反馈。

/cfs-file/__key/communityserver-discussions-components-files/196/TPS56628DDA_5F00_5V.brd

谢谢

您好、

请查看我关于5Vout 电源轨的评论:

SCh:

- EN:由于 EN 引脚为高电平有效、请确保电源连接得足够高、否则器件将无法开启。 您将 EN 电阻器 R1955和 R1956作为 DNP、这就是我记下这一点的原因。 如果您要使用 VCC_REG3_IN 来 实现启用、则可能需要一个0欧姆电阻器而不是 R1955的 DNP、以确保连接。 如果您有噪声源/周围、或者您认为 EN 会低于阈值、最好添加一个上拉电阻器。 我们的原理图使用10k Ω 电阻器。

- PG : RPG 电阻值,连接在 PG 和 VREG5之间,需要25k Ω 到150k Ω 之间。 您当前使其为0欧姆。 对于 R407、它的用途是什么? 没有标准设计、就可以正常工作。

- Cff (C1666 ):顶部 FB R 之间的电容应该在1 - 22pF 范围内,你目前有它作为 DNP 但值是150pF ,最好是保持在推荐范围内根据表1在 DS 以确保稳定性。

布局:

-无法打开文件,因为错误:

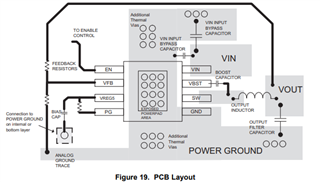

但是、您可以检查主要布局项目:

-为了散热目的,保持 GND 平面低于 IC

-保持电流回路短路(SW/VIN/COUT)

-即使器件没有 AGND 引脚,您仍需要将模拟(EN/VB/VREG5/GNO) PG 的接地与电源信号(其余引脚)隔离。

-确保元件靠近 IC、特别是电容器、fb 电阻器、引导电容器和 vreg 电容器。

此致、

Eileen