工具/软件:

您好、

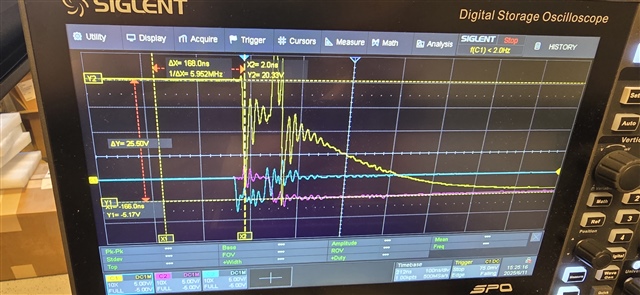

我们已经确定了栅极驱动器故障的根本原因。 下面的波形捕获显示 OUT(黄色)、EN(蓝色)和 IN+(品红色)。

对测量中的噪声表示歉意、但 EN 和 IN+之间的短暂重叠(大约 10–13ns)似乎足以损坏驱动器。

具体情况如下:

-

故障检测电路将 EN 拉至低电平、禁用驱动器。

-

~62ns 后、EN 再次变为高电平。

-

由于传播延迟(例如,通过隔离器~75ns) 、 在 EN 重新激活后、IN+在~10–13ns 内保持高电平。

这个短暂的重叠周期(EN 和 IN+均为高电平)似乎持续损坏驱动器。 发生此类事件后、器件会永久损坏、VDD 和 GND 之间的电阻通常测量的 18Ω 约为 60Ω 。