请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

零件号:ISO5852S 工具/软件:

尊敬的团队:

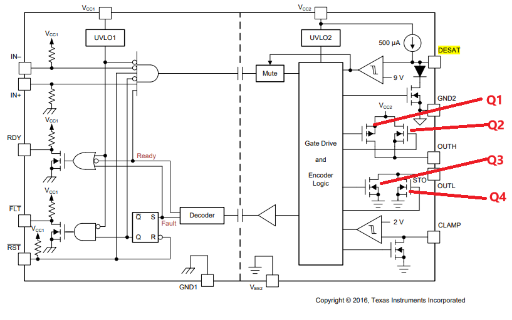

客户使用 ISO5852 时、他对内部方框图有以下问题、您能在此处提供专业的解释吗? 提前感谢。

- 当逻辑 H 时、Q2 导通、Q1 的作用是什么? 何时打开?

- 正常逻辑 L 时 Q3 导通、而过流软关断时 Q4 导通。 Q3 和 Q4 之间的驱动电路差异或驱动电路差异是什么?

BRS、

Francis

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

工具/软件:

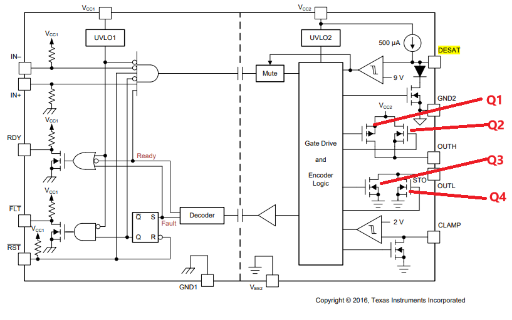

尊敬的团队:

客户使用 ISO5852 时、他对内部方框图有以下问题、您能在此处提供专业的解释吗? 提前感谢。

BRS、

Francis