工具/软件:

尊敬的 TI:

我想确认器件在短路时的行为。

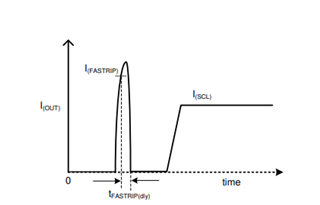

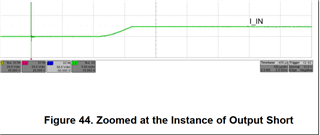

采用电子保险丝的方式是、使输出端会因容性负载而出现瞬时浪涌、并触发短路保护。

然后、当电子保险丝启动时、输出电压将充电、但该速率低于我的预期。

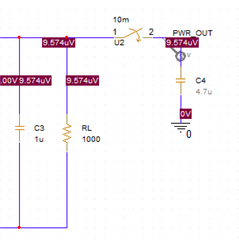

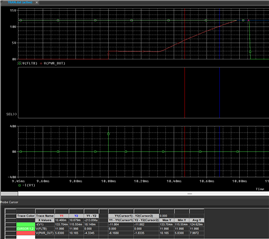

我使用修改后的参考仿真文件运行仿真、并添加了开关和容性负载来模拟浪涌

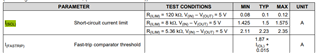

结果表明、当我的电阻器设置为 62k Ω 时、为电容器充电的电流仅为 133mA、应该可得到~0.2A 的电流。

我曾尝试使用其他电阻器阻值、但电流始终限制在~0.13A 范围内

从该图中、我可以预期电流会根据电阻器受到限制、是不是出现了问题?

此外、另一个 queston 是、即使 PWR_OUT 达到 12V、FLTB 仍有效。 这也是预料之中的吗? 我希望在清除故障(本例中的电流受限)后计时器停止。