您好、

请帮助您澄清 TPS259480AYWP 中未激活时的 SPLYGD(非反相)引脚电压电平。

这是一个 OD 信号、当 输入电源有效且通道已 完成浪涌序列时、该信号被置为高电平。

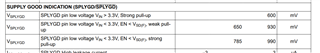

在以下情况下、Vol_max 应该是什么?

如何估算 Vol 的强或弱 PU 值?

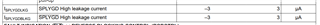

IQ 电流+–3uA 是否与高电平有效状态相关?

SPLYGD 音量=? VIN = 0V、强上拉

SPLYGD 音量=? Vin > 3.3V、强上拉

SPLYGD 音量=? Vin >3.3V、弱上拉

SPLYGD 音量=? VIN < 3.3V、强上拉

SPLYGD 音量=? VIN < 3.3V、弱上拉

我将与大家分享基于 SPLYGD 信号和具有高 Vgs_th 的 N 沟道 MOSFET 的实现方案。

e2e.ti.com/.../USB_5F00_2.0_5F00_EN-mechanism.ppt

此致

Vitaliy