主题中讨论的其他器件:LM74800EVM-CS

工具/软件:

您好:

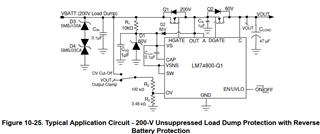

我们的实际设计针对 24V 系统使用数据表中所示的共源拓扑来确定尺寸:

数据表的第 10.3.2 章给出了设计过程。 在“10.3.2.7 MOSFET Q2 选择“一章中、 根据设计要求选择了 MOSFET BUK7Y4R8-60E。 这是一款 60V-FET 、与未抑制负载突降保护评估模块 LM74800EVM-CS、SLVUBU4 中使用的 FET 相同。

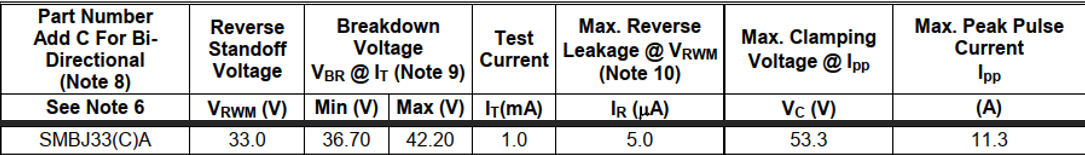

输入电压抑制由 D3: SMBJ150A 与 D4:SMBJ33CA 串联实现 。

ISO 7637-2 脉冲 1(–600V 50 Ω、持续 1ms) 会产生约 3.5V ( SMBJ150A 的 Vf)+ 53.3V ( SMBJ33CA 的 Vc)= 57V 的输入钳位电压

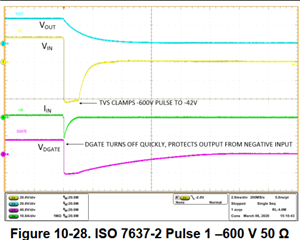

数据表中的图 10-28 显示了测试结果:

但是、在 ISO 7637-2 脉冲 1(–600V 50 Ω 持续 1ms) 的情况下、最大 超出 Q2 的 VDS: 电压 (C-A)= VDS (Q2) = 24V + 57V = 81V。

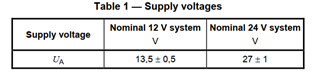

ISO 7637-2 的测试规范使用 更大的电源电压值:最大 24V 系统为 28V:

因此、电压 (C-A)= VDS (Q2)= 28V + 57V = 85V。

我的问题:这里为什么选择 60V FET?

对我来说、这次唯一的解释是这里假设 Q2 的某个雪崩额定值能够承受、但我在数据表中找不到这样的考虑因素。

目前、我们使用的 FET Q2 = ISC0703NLSATMA1、这也是一款 60V FET、但其雪崩额定值比 BUK7Y4R8-60E 低得多。

主要选择它来实现高达 200kHz 的有源整流、这是 BUK7Y4R8-60E 无法实现的。

PCB 处于样片生产状态、因此如果我们需要采用其他封装的 FET、则必须重新设计。

此致、Oliver。