工具/软件:

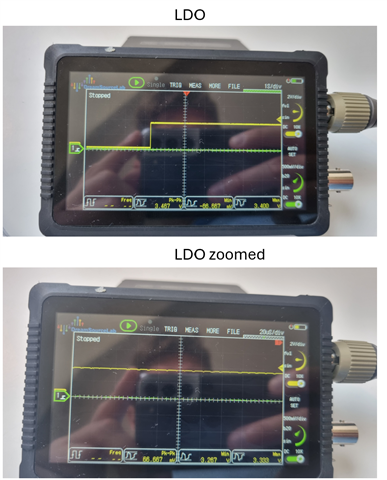

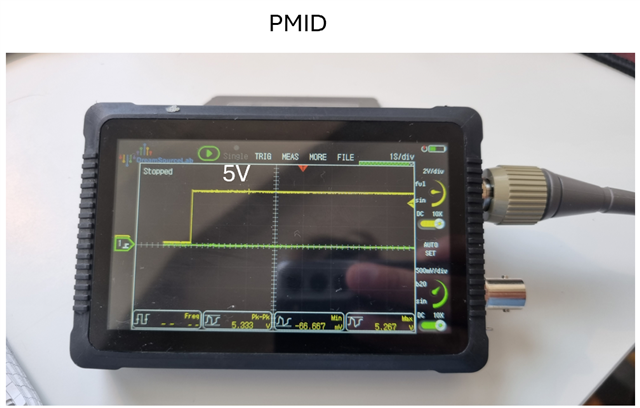

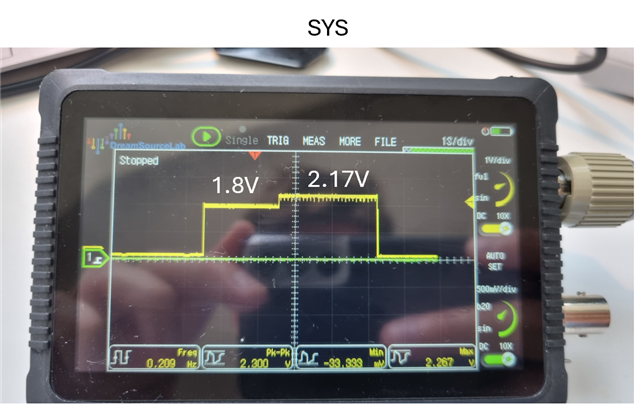

我努力使 SYS 正常工作、我需要默认的 1.8V、并且电压突然增加到 2.5V(未连接 VIN)或 3.6V(连接 VIN)之前、似乎会在一小段时间内产生这种情况。 似乎没有任何错误消息、这些是我的寄存器值。 我将 0x01 放入 0x04、因为它在断开输入电压后生成了 VIN_UV:

寄存器 0x00 值:0x41

寄存器 0x01 值:0x04

寄存器 0x02 值:0x08

寄存器 0x03 值:0x14

寄存器 0x04 值:0x0E

寄存器 0x05 值:0x78

寄存器 0x06 值:0xAA

寄存器 0x07 值:0x7C