工具/软件:

您好:

我提出了一个使用 12 个 TPS1HTC30-Q1 作为高侧负载开关的设计。 这些器件表现出与数据表不匹配的行为、我希望能就可能发生的情况提供一些意见。

我的电路板上的所有实例都是一样的、因此这不是一个部件损坏的问题。 PCBA 也直接来自汇编器、只能在 ESD 安全环境中进行处理。 我还确认了引脚排列正确、器件标识与数据表相匹配、元件方向正确、并且没有短路。

我的测试配置如下:

- 28V 电源

- EN 由微控制器通过 10k 串联电阻器拉至低电平

- ILIM 引脚上为 24.9K(对于 4A 设定点)

- SNS 引脚上为 768R

- LATCH 连接到 GND

- DIAG_EN 连接到 3.3V

- nFAULT 上的 100k 上拉

- 未连接负载(起始)

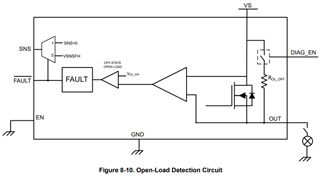

首次为 PCBA 通电时、我注意到使用热像仪时、所有 TPS 器件都在比环境温度高约 10ºC μ A 的温度下升温。 在进一步调查时、我测得 VOUT 引脚的电压高 330mV(!!!) 低电源电压。 nFAULT 被拉至低电平、与开路负载检测一致、但 SNS 引脚的读数为 3.47V、表明电流检测读数约为 6A。 (同样,没有负载,流入电路板的总电流远小于 1A。) 也不应可能出现 SNS 电压、因为数据表指示它不会超过 3.3V 的 DIAG_EN 电压

当我将 22R 负载电阻器连接到输出端时、该器件似乎运行正常。 发热停止、从 28V 电源汲取的电流约下降了 7mA。 SNS 引脚现在的读数为 0、并且 nFAULT 被置为无效。

除了 TPS1HTC30s 中用于内部栅极驱动器的升压转换器或电荷泵之外、我的设计没有升压转换器或电荷泵。 我的假设是、电荷泵输出以某种方式到达 VOUT 引脚并经过内部 MOSFET 的体二极管、但基于简单的内部方框图和数据表中真正不应该提供的所有信息。

我将继续研究 — 包括查看当我将 EN 置为高电平时会发生的情况(需要先进行一些固件更改,然后我才能这样做)-但现在想把它放在那里、以防有人看到任何类似的东西。

谢谢!