工具/软件:

尊敬的团队:

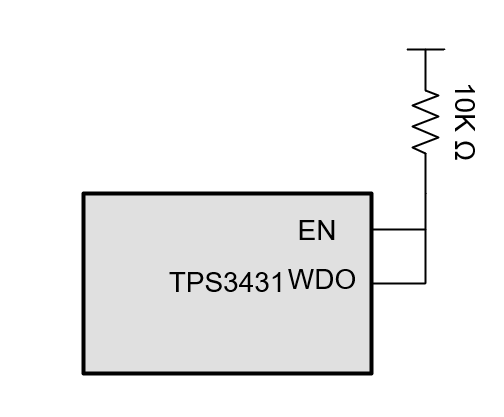

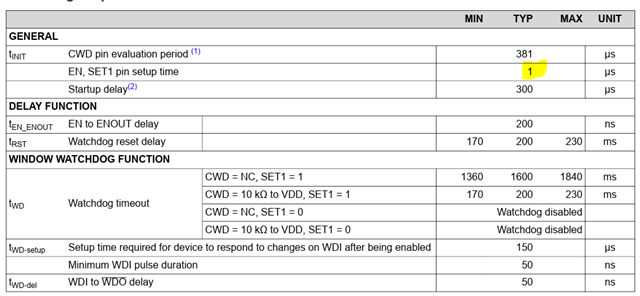

我们在设计中使用的是 TPS3431SDRBR 看门狗、如下图所示。 SET1 和 WDI 引脚由 CPU 控制、CWD 引脚生成 900 毫秒(最大值) 使用 10nF 电容器时的看门狗超时 (TWD)。

WDO 引脚连接到 CPU RESET 引脚 POR_X、SET1 引脚下拉。

测试观察:

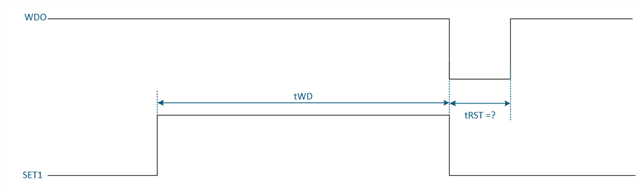

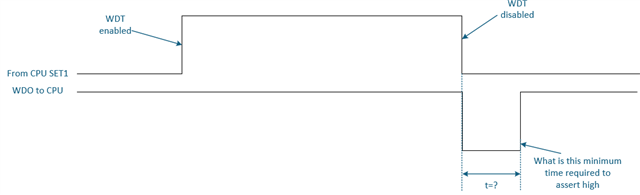

通过将 SET1 引脚设置为高电平并且未应用 WDI 脉冲来启用 WDT、在 834ms WDO 置为低电平且 CPU 复位后、因此禁用看门狗、并且由于此复位延迟时间 (TRST) 仅在 100us 内保持低电平。

问题 1: 在上述配置下、最短复位延迟时间 (TRST) 是多少。

问题 2: 是否可以小于 100us? (例如 1us 或 10us 等)

有关波形的详细信息、请参阅随附的文件。

e2e.ti.com/.../TRST_5F00_Watchdog.docx

此致、

Sanju