主题中讨论的其他器件:LMZ23605

工具/软件:

我使用的是 LMR36503RS3QRPERQ1 IC。

通过在 RT 引脚上连接 41.2K Ω、将频率设置为 400kHz。

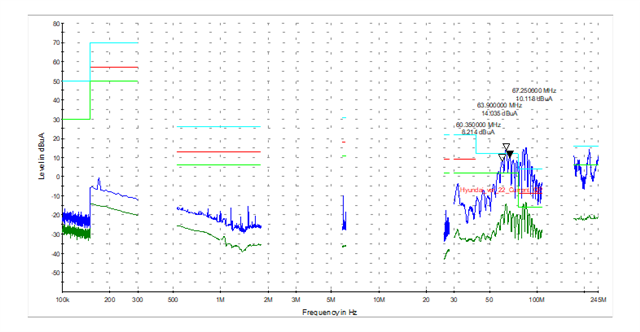

我确认工作频率为 60~70 kHz、而不是 400kHz、因为降压 IC 后面连接的负载很小。

参考 AN-2162 文档设计 CLC 滤波器时、应该使用哪个 FS 值、400kHz 或 60kHz?

如何找到 Vin-ripple P2 值?

您能否详细说明示例 1 (LMZ23605) 中的“CFB"值“值的计算过程?