工具/软件:

您好:

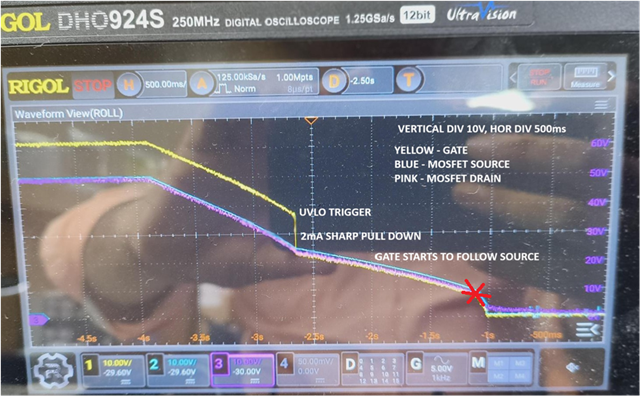

我们使用 LM5069 使用 CSD19502 MOSFET 和 12m Ω 感测电阻将 48V 切换为高电容输出 (~2.5mF)。 启动时没有负载、电容除外。

该设计使用带 0.1uF 电容的 dv/dt 控制和数据表中所示的 PNP 放电电路。 但是、在极少数情况下、我们会看到 GATE 引脚上还残留电荷、从而导致 MOSFET 在系统断电后的几小时内表现出低电阻(10-100 Ω)。 这在探测栅极引脚时会耗散、再次正常工作。

但是、数据表显示了 GATE 引脚上的 2mA 下拉电阻。

如有遗漏、请告知我们。 如有需要、可以在专用窗口中共享电路以供查看。

此致

Gaurav