工具/软件:

您好的团队、

下冲约为–0.5V、持续 20ns。

这是否可以接受?

此外、它在多大程度上可以接受?

此致、

Ryu。

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

工具/软件:

您好的团队、

下冲约为–0.5V、持续 20ns。

这是否可以接受?

此外、它在多大程度上可以接受?

此致、

Ryu。

您好、Ryu、

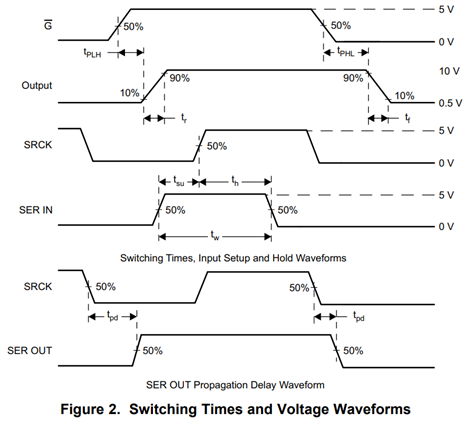

是指输出漏极电压下冲吗? 我看到上升 (tr) 时间和下降 (tf) 时间分别为 210ns 和 128ns。 这是在转换期间达到预期电压的 90%或 10%的时间。 这段时间内是下冲吗?

您能否更具体地说明哪个信号或显示波形? 我没有关于电压欠冲的具体信息、但可以根据需要在 EVM 上对其进行采样。

有关典型的开关波形、请参阅下图:

此致、

以赛亚书

您好、Ryu、

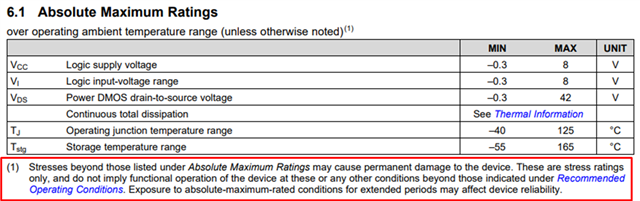

关于违反绝对最大额定值的唯一指导原则是数据表中表 6.1 的脚注 (1)。 我们不能就是否会造成损坏的确切持续时间提供指导。

Isaiah 建议使用尖端和接地筒探头进行测量、以确保下冲是真实的、而不是传统示波器探头中接地环路引起的干扰。 您还可以检查探头补偿、查看探头本身是否表现出下冲/过冲行为。

https://resources.pcb.cadence.com/blog/what-is-oscilloscope-probe-compensation

如果您可以使用尖头和桶形探头测量来确定下冲是真实的、 我建议遵循以赛亚的建议、在数字线路上添加一些串联电阻以减少下冲。

此致、

Zach