主题中讨论的其他器件: LMZM33606

工具/软件:

您好、

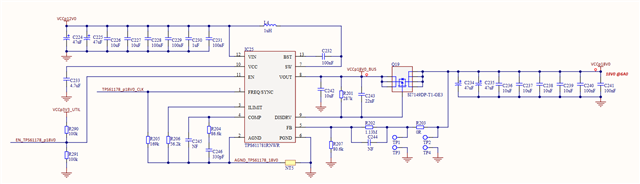

按照以下原理图片段、我们在设计中使用了 TPS611781RNWR、以便从 12V 电压轨生成 18V 电压。 EN 由 GPIO 控制。 我们已经看到、从 EN 变为高电平到 TPS611781 启动的延迟相当长、根据以下测量结果、延迟约为 90ms。

EN ->启动时间是恒定的已知数字吗? 我在数据表中看不到。

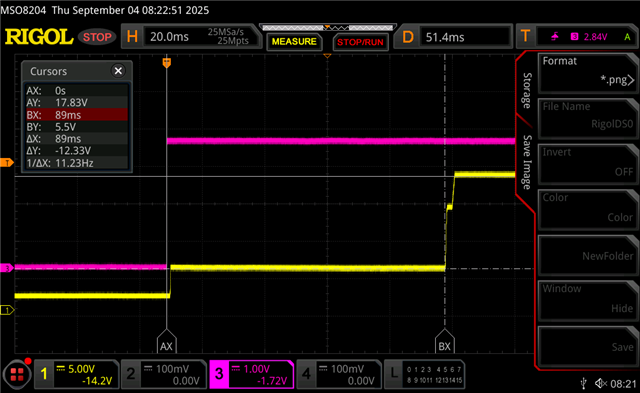

EN ->输出测量

黄色迹线 (Ch1) 是 VCCp18V0 电源轨(TPS61178 的输出)。

粉色迹线 (Ch3) 是 EN 信号

当 EN 为低电平时、VCCp18V0 电源轨约为 2V。 当 EN 变为高电平时、VCCp18V0 电源轨上升到中间 5.5V 电平。 EN 信号变为高电平 89ms 后、TPS611781 似乎开始正确启动、这需要~3ms 才能完成。 然后 VCCp18V0 电源轨达到 18V。

原理图