工具/软件:

您好、

我们使用 LM74502QDDFRQ1 IC 来驱动两个背对背连接的 NMOSFET (NVMFS5C673NLAFT1G)、其输入电容 (CISS) 为 880 pF。 我们选择了 10nF 的 VCAP 电容器、输入电源电压为 14V

但是、我们观察到、IC 需要大约 1ms 的时间使 VEN 信号栅极上升。 您能帮助我们了解如何缩短上升时间吗?

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

工具/软件:

您好、

我们使用 LM74502QDDFRQ1 IC 来驱动两个背对背连接的 NMOSFET (NVMFS5C673NLAFT1G)、其输入电容 (CISS) 为 880 pF。 我们选择了 10nF 的 VCAP 电容器、输入电源电压为 14V

但是、我们观察到、IC 需要大约 1ms 的时间使 VEN 信号栅极上升。 您能帮助我们了解如何缩短上升时间吗?

尊敬的 Shiven Dhir:

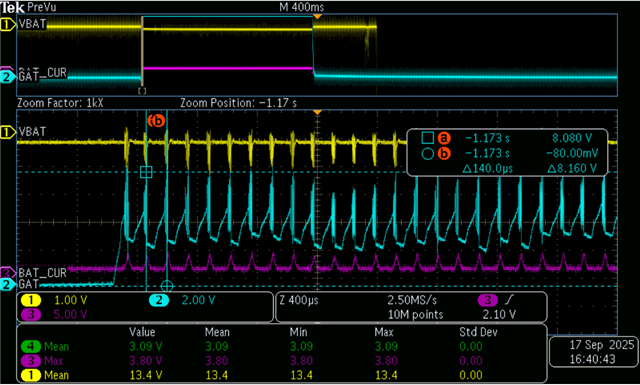

我们将 VCAP 电容器更新为 0.22 µF 。 不过、我们观察到了栅极电压最初无法完全导通的问题。 它最初脉冲至 8V 左右 、只有一段时间后才会完全上升至 23V

我们已将 OV 连接至 GND 和 VS - 13.5V。

已附上图像以供参考。

我们还尝试进一步降低 VCAP 值、但问题仍然存在。

请帮助我们纠正此问题。

谢谢你。

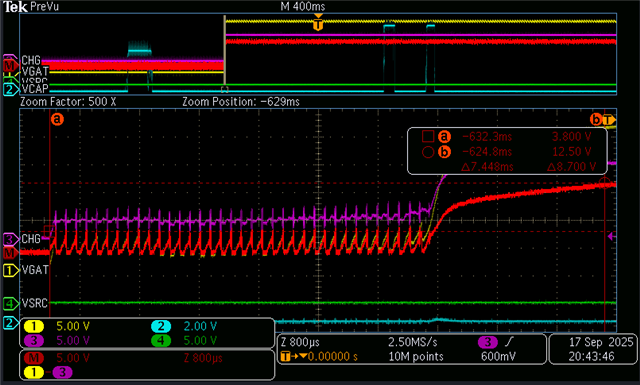

尊敬的 Shiven Dhir 、

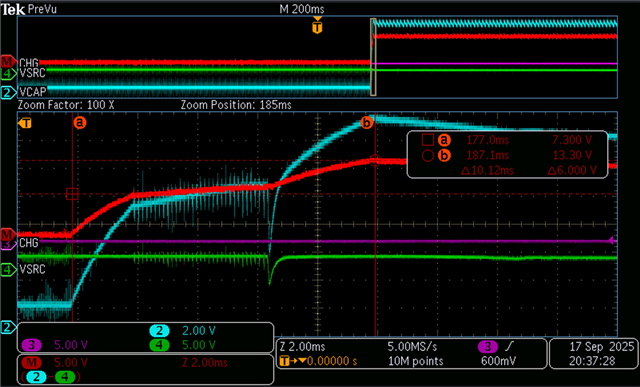

请找到随附的图像以供参考。

以下探测期间使用的 VCAP 为 0.1uF

1) 在栅极脉冲时间的 VCAP-VS 电压约为 7V(红色通道: VCAP - VS)

2) 其中作为 GATE-SRC 电压约为 3.8V (红色通道: VGATE-VSRC)

请分享您对此的想法。

谢谢您、

Jeevabharathi

尊敬的 Shiven Dhir:

由于我们目前处于评估阶段、因此尚未提供详细的原理图。 不过、我可以分享一下在我们的验证过程中使用的粗略电路图。 请找到随附的图像以供参考。

期待您的答复。

谢谢您、

Jeeva.

尊敬的 Shiven Dhir:

您能帮助我们了解 VCAP 低于 0.1uF 时可能会发生什么情况吗?

谢谢、

Jeeva.