Other Parts Discussed in Thread: TPS25910, TUSB211, HD3SS3220, 3220DFP-DGLEVM, TUSB211A, CSD17313Q2, TPD1E05U06

主题中讨论的其他器件: 3220DFP-DGLEVM、TPS25910、 TUSB211A、TUSB211、 CSD17313Q2TPD1E05U06

工具/软件:

尊敬的专家:

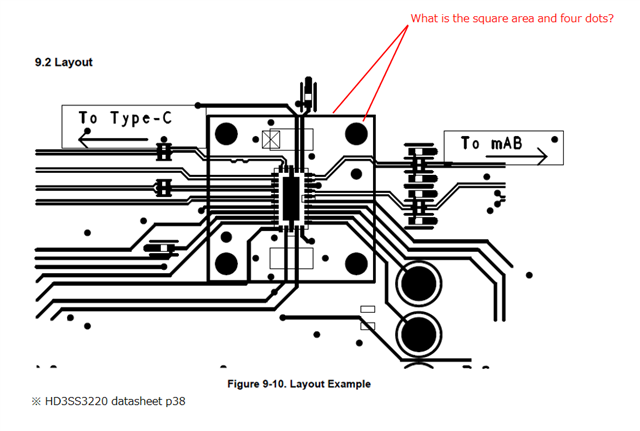

我的客户正在考虑使用 HD3SS3220、并需要审查原理图。

请 查看随附的 Excel 文件并提供您的建议。

如果您需要其他信息、请告诉我。

e2e.ti.com/.../Question-about-HD3SS3220-20250814-.xlsx

感谢您提前提供的大力帮助。

此致、

Shinichi