工具/软件:

您好、

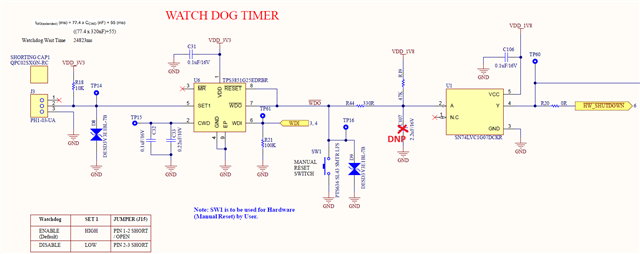

我使用以下电路布局测量 TPS3851 的 WDO 引脚 (tRST) 上的低电平输出持续时间:

WDO 引脚上的预期低电平脉冲应约为 200ms 的低电平脉冲、但我只获得了 124ms 的低电平脉冲。

原因可能是什么? tRST 不能以任何方式配置、所以为什么我看到的持续时间只有 120ms、而不是 200ms? 非常感谢您对此提供宝贵反馈。 谢谢。

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

工具/软件:

您好、

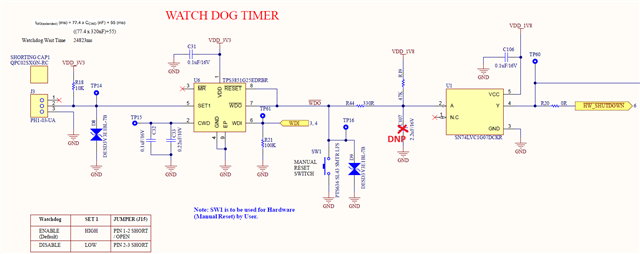

我使用以下电路布局测量 TPS3851 的 WDO 引脚 (tRST) 上的低电平输出持续时间:

WDO 引脚上的预期低电平脉冲应约为 200ms 的低电平脉冲、但我只获得了 124ms 的低电平脉冲。

原因可能是什么? tRST 不能以任何方式配置、所以为什么我看到的持续时间只有 120ms、而不是 200ms? 非常感谢您对此提供宝贵反馈。 谢谢。

您好 Sila、感谢您的答复。 观察结果:

1) 到目前为止,我们还没有尝试用相同 IC 的另一个样本替换。 我们将尽早在此处更新。

2) 输出变为逻辑低电平的原因 将始终为 WDO 且从不复位(因为 3.3V VCC 稳定)。 我们已在 RESET 和 WDO 引脚之间填充并取消填充 0r、但结果仍然相同。 因此、根据我们的观察、无论 RESET 引脚是否与 WDO 短路、都没有关系。 输出低电平应始终为 200ms 的逻辑低电平、但这不是我们在这里看到的结果。 希望这有所帮助。 谢谢。

你好、Vishrut、

感谢您使用另一个 IC 进行测试。 请分享一下 ESD 袋的图像。 批号和 组装地点 (ASO) 会在发货/包装盒标签上注明。

在下一步中、您能否将 CWD 配置更改为 CWD = 10kΩ to VDD、SET1 = 1 并测量最长和最长时序? 这样、我们可以确认时序问题是否 与另一个配置重复。 还请分享 具有 WDI、WDO 和 HW_SHUTDOWN 的示波器图片。

我将订购您的器件型号 TPS3851G25EDRBR、以测试我是否会再次出现此问题。 我可能需要 3-5 天才能收到 IC。

有关原理图的侧边反馈:您可以将 SW1 连接到 MR 引脚、而不是将其置于复位状态。 MR 引脚是 MANUEL RESET 引脚、只要它为低电平、RESET 就会被置为有效。

谢谢、

Sila.