Other Parts Discussed in Thread: PMP22806, TPS23731, UCC24612

主题中讨论的其他器件:PMP22806、 UCC24612

工具/软件:

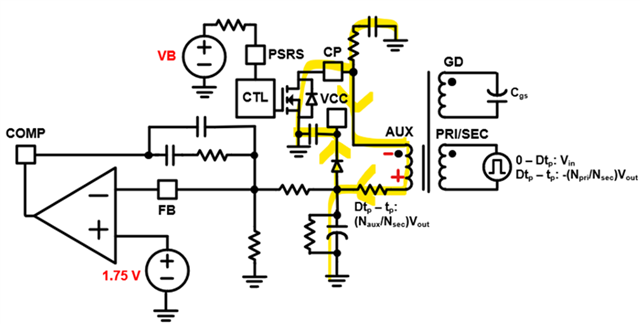

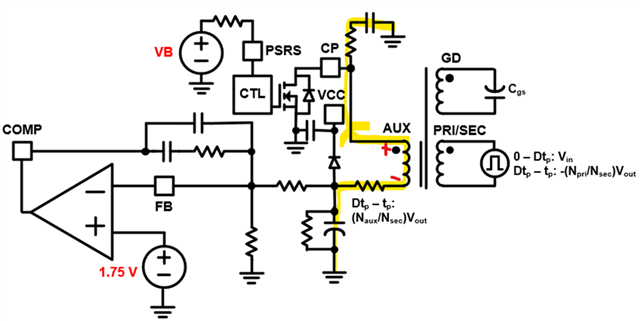

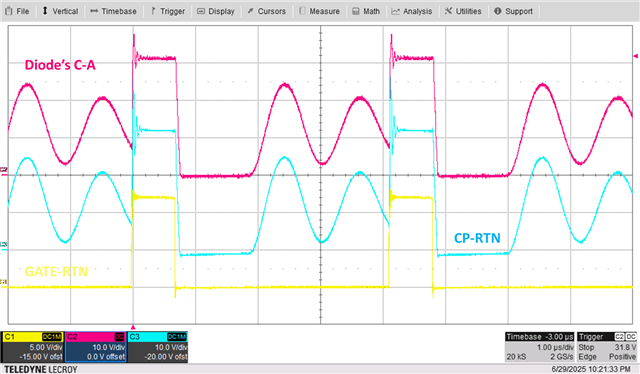

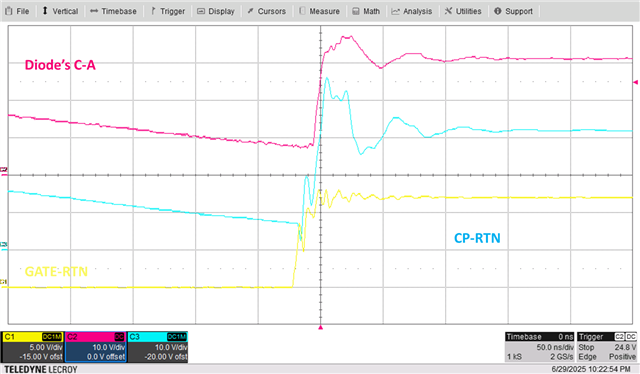

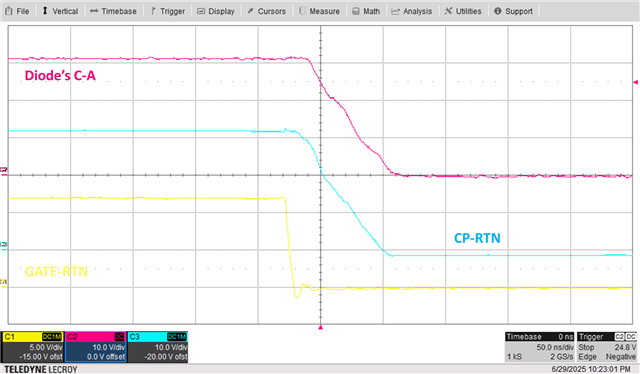

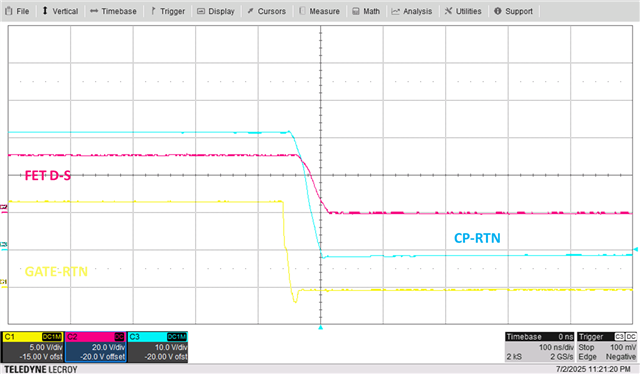

在相关主题(原始问题)中、我质疑是否 可以真正假定“主动消除(通过使用 CP 输出)前沿电压过冲(使反馈电容器达到峰值电荷)“。 因为一旦初级 MOSFET 关断、体二极管就会立即导通、而漏电感尖峰会暴露在反馈电容器上。 但必然结果是:只有在 CP-MOSFET 导通有很小的延迟时、标称绕组电压才不会向电容器注入电流、因为在上一个周期中、电容器会在初级开关关断状态下通过绕组电压减去 CP 端子后面“理想二极管“上的最小压降进行充电。 下一个周期开始时、只有体二极管导通、并且由于电容器的电压下降没有超过几 mV、电容器的“可用“净电压较低:绕组电压减去体二极管。 因此在这个最短的时间间隔内、漏电感尖峰可能会注入一些电流(受串联电阻限制)、但没有影响。 因此、电容器电压非常准确地检测净绕组电压。

但根据我的实验、似乎任何延迟都难以察觉。 也许任何 TI 员工都可以给出具体的说明。 当然、延迟应比尖峰宽度长、以获得出色的负载调节性能。

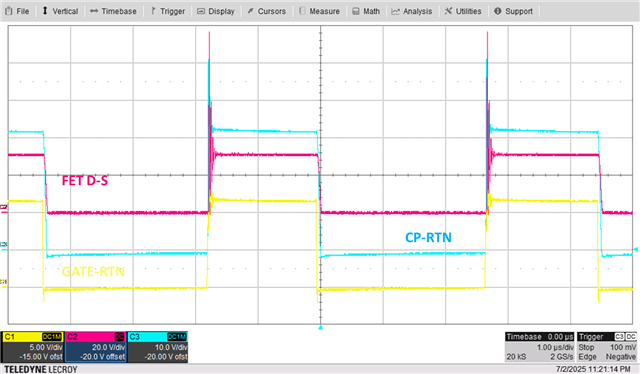

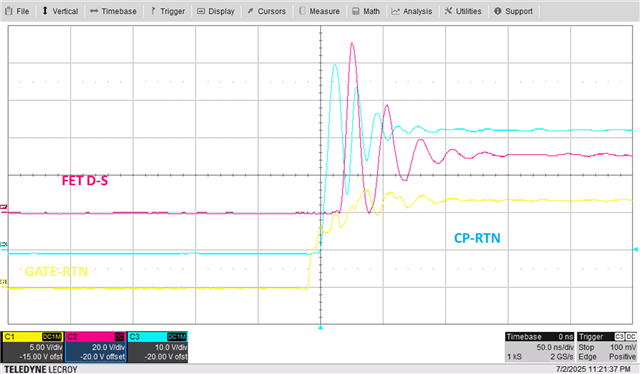

如果次级侧的理想二极管电路用作整流器、上述说明也有助于实现良好的负载调节。 输出电压(理想情况下)基于理想二极管电路的 MOSFET 导通时次级绕组电压的调节。 但是、在 MOSFET 关断之前的初始延迟(例如 40ns)内、次级绕组电压会高出约 0.6V。 这反映在辅助(和初级)绕组中。 这将很好地增加反馈电容器电压(有效地降低输出电压)。 但是、如果 CP-MOSFET 的延迟也不会小于次级侧延迟、那么该效应实际上将被中和。

因此、更有趣的是、了解 CP-MOSFET 导通延迟。

下一个问题:应用到 PSRS 的定时控制信号是否会强制进行额外的 CP-MOSFET 延迟? 当 PSRS 上的电压设为低电平时、CP MOSFET 是否过早停止导通? 简而言之:跟随 CP 电压的信号、向正电压范围偏移并延迟到 PSRS 正斜率。 简单地说:PSRS 是否可以由数字信号“调制“、或者 PSRS 后面的内置触发器是否无法实现连续的数字控制?