工具/软件:

您好、

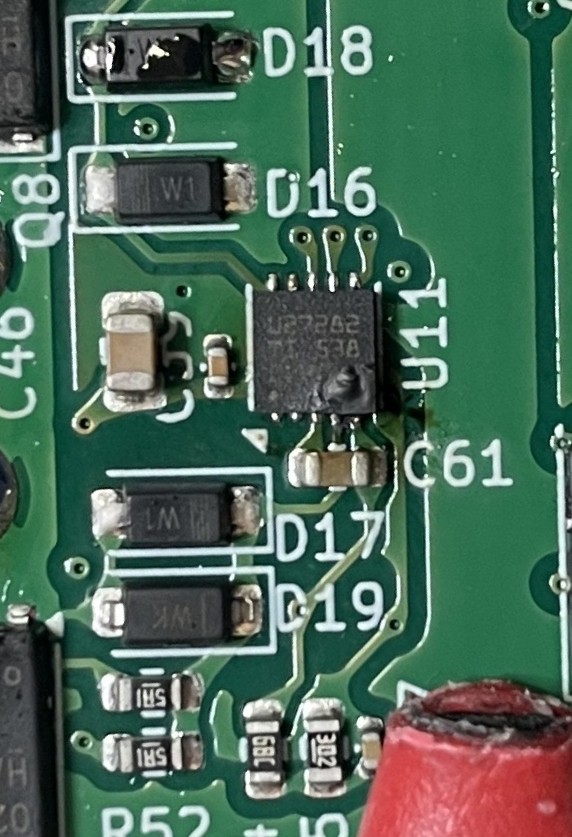

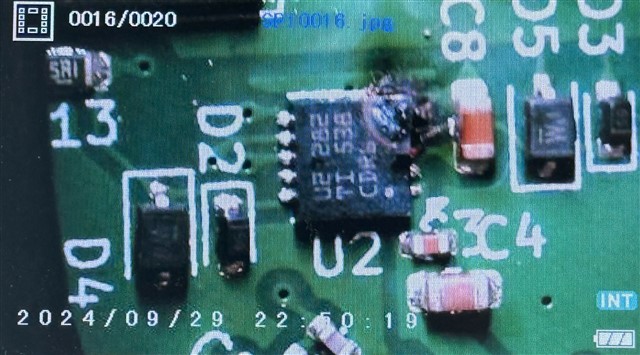

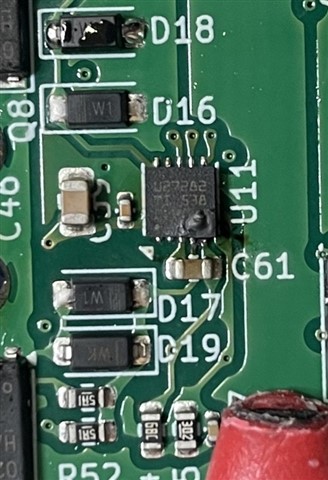

最近 UCC27282DRCR 栅极驱动器发生 3 次故障、所有外部故障似乎都发生了故障、并在同一位置(引脚 4 和 5 附近的角落)烧了驱动器。

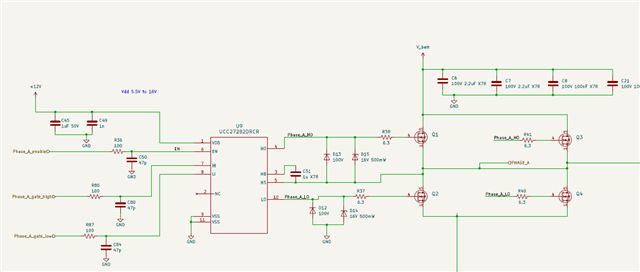

原理图:

未显示;低侧分流电阻 1.5mΩ,电压感测 HS 50k 阻抗

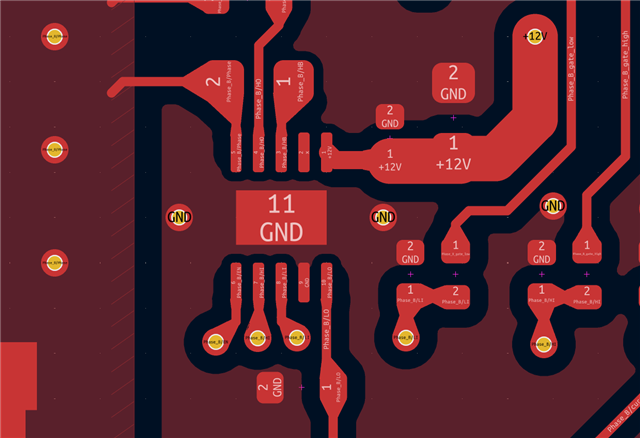

顶层布局

应用适用于具有~50V V_batt、PWM 频率 20kHz(中心对齐)的电机驱动器。

MOSFET: BSC026N08NS5ATMA1

D12/D13(欠压肖特基保护): BAT46X (100V 1V@ 250mA SOD-523)

D14/D15(过压齐纳二极管): BZT52C15S-7-F(齐纳二极管 15V 200mW SOD-323)

占空比在软件中被限制为最大 95%

这两个故障似乎都是零星的、始终运行良好、然后发生故障。 我没有任何故障示波器屏幕截图。 一种情况下、高侧 MOSFET 也发生短路故障、另一种情况下、驱动器发生故障。

我知道旁路电容器的尺寸过小、但 在 48V -> 12V 降压转换器的输出端、靠近驱动器有 10uF 和 2.2uF 电容器。