工具/软件:

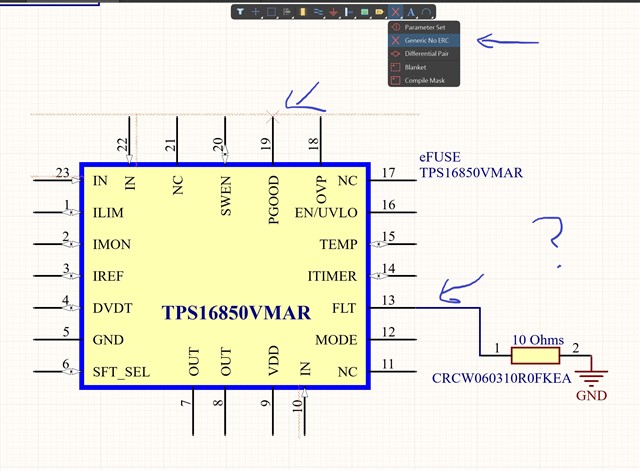

你好,我正在使用这个新的电子保险丝。 我仍然不知道我需要把它放在引脚 19 PGOOD 和引脚 13 FLT 上,我一直在问不同的 AI ,大多数不是一个可靠的答案,我的意思是一些 AI 说它可以是一个指示灯。

我想知道我是否需要将其与电阻器连接、或者是否需要将其留空。 有人说 FLT 至少应连接 10kΩ 到某个有 3.3V 或 5V 的地方,我仍然没有得到它。

PGOOD>>这是一个开漏高电平有效电源正常引脚、在该引脚上被置为高电平有效

器件处于稳定状态。 该引脚有一个到内部的弱内部上拉电阻

电源电压。

FLT>>这是一个开漏低电平有效引脚、拉低时会指示故障。 拉动

使用一个电阻器将该引脚上拉至外部电源。

我还不知道这是什么意思吗?