将 TPS65217CRSLT 与 AM3358BZCZA100 UP 和 ISSI IS46TR16640B-125JBLA2 DDR 存储器配合使用。

系统中没有电池、使用应用 SLVA901、我们使用系统稳压 5V 作为直流/直流降压电源的 VIN、并使用从 BAT/ BAT_SENSE 到接地的 100 Ω RLL。 VIO 由 VLDO2 供电。 L1、 L2 和 L3 上的每个都有 2.2uH 电感器。 此外、L1 具有 30.1uF(3 个 10uF 和 1 个 100nF 并联)输出电容、而 L2 和 L3 每个具有 20.1。

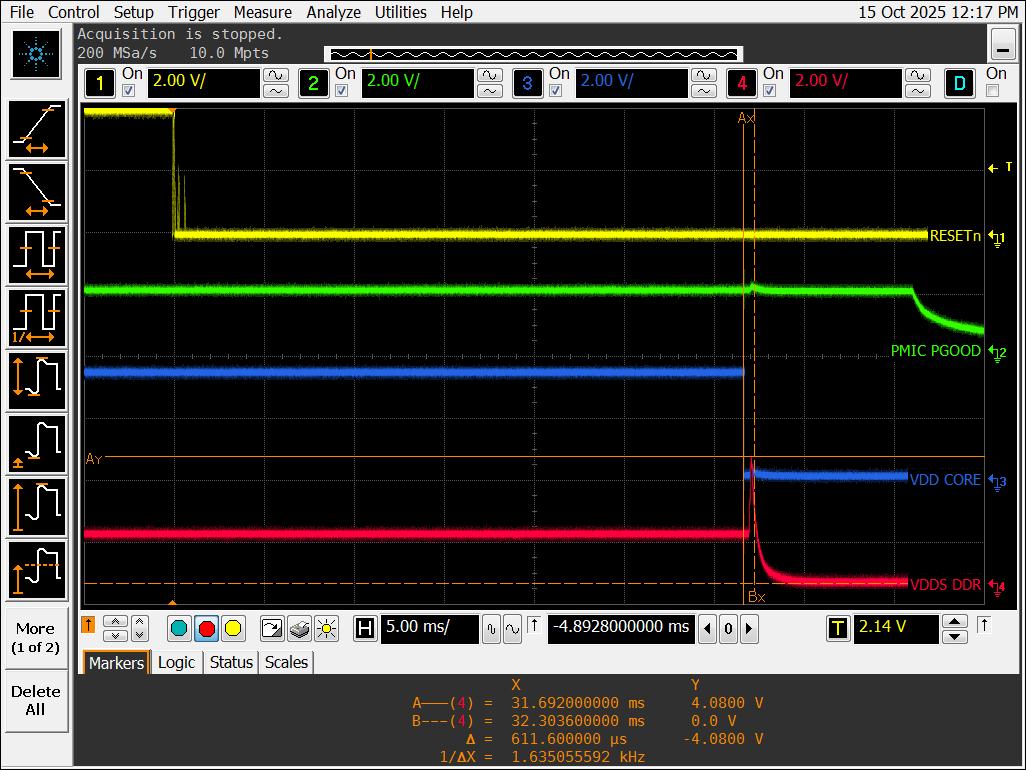

通常、RESET_N 保持开路、因为我们在默认条件下使用 PMIC、并且不会通过 I2C 进行通信。 然而、在我们模块的钉床测试期间、我们发现在将复位下拉至将 DCDC1 输出尖峰从 1.5V 拉至 4.08V 时、便会关闭、并导致许多 DDR 器件严重损坏。 PMIC DCDC1 和 DDR 之间有 0 Ω 链路电阻器、在移除这些电阻器后、PMIC 出现问题后、尖峰仍然存在。

什么可能导致 DCDC1 输出出现此尖峰?