《线程》中讨论的其他部件:OPA2374, 测试

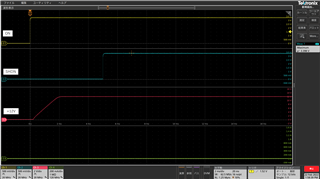

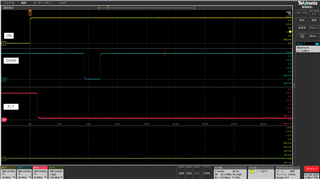

在启动计时上,/FLT 输出断言“低”(可能是 UVLO),尽管/sHDN“低”⇒“高”,但未释放到“高”。

请告诉我以下两点:

・锁扣重新启动的正时或其他条件(/FLT 至 HIGH)

・如果以下连接错误或任何故障输出情况建议,请告诉我。

【信息】

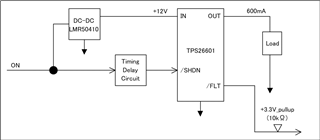

・连接图附在下面。

正时延迟电路基于 OPAMP (OPA2374),以便在+12V 启动后使/FLT 输出重置的时间延迟。

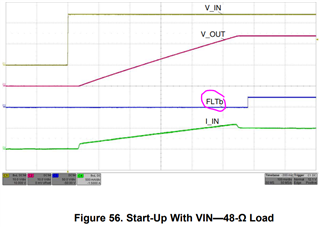

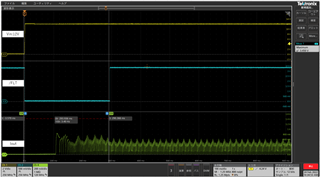

・以下是波形,请忽略 CH4波形。

・关于高/低/高的 SHDN 时间⇒⇒高;当低任期设置太长:0.5秒和1秒时,/FLT 也保持低。

・当更改为 TPS26602 (自动重试)时,/FLT 输出在启动后变得较高。

但一位客户需要使用 TPS26601的锁存功能。

我们希望 TPS26601能够解决这个问题。

此致,

萨特希