您好,

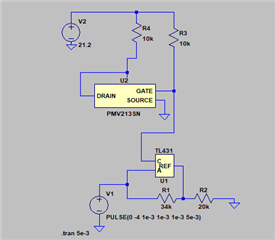

我正在使用 TL431QDBZR 分流调节器和 NMOS 晶体管(NMOS 的排放引脚以启用电路)。

案例1 -使用 Vin=-5V 和电阻器分隔器 ckt b/w 参考引脚和阳极(R1 = 24.9K,R2 = 20K),Vref =-2.227V,小于 int Vref = 2.495V。 NMOS 变低,通过上拉电阻器(即21V)将排卸拉高

案例2 -如果我使用具有-4V 电源的相同电阻器分压器电路,节点处的 Vref =-1.782V,这再次低于 int Vref,但 NMOS 被拉高,排卸被拉低至地电位。

案例3-但如果我将24.9K 值更改为34K 值,则 Vref 更改为-1.5V,NMOS 关闭,并通过上拉电阻器将漏极高。

我的问题是为什么 NMOS 在案例2中处于高位而在案例3中处于非高位,尽管案例3节点处的 Vref 高于 案例2?

谢谢

丹维尔