主题:TPS7A47中讨论的其它部件

使用TPS7A系列为以下每个原理图片段提供经调节的低噪声对称(+/-24VDC)输出:

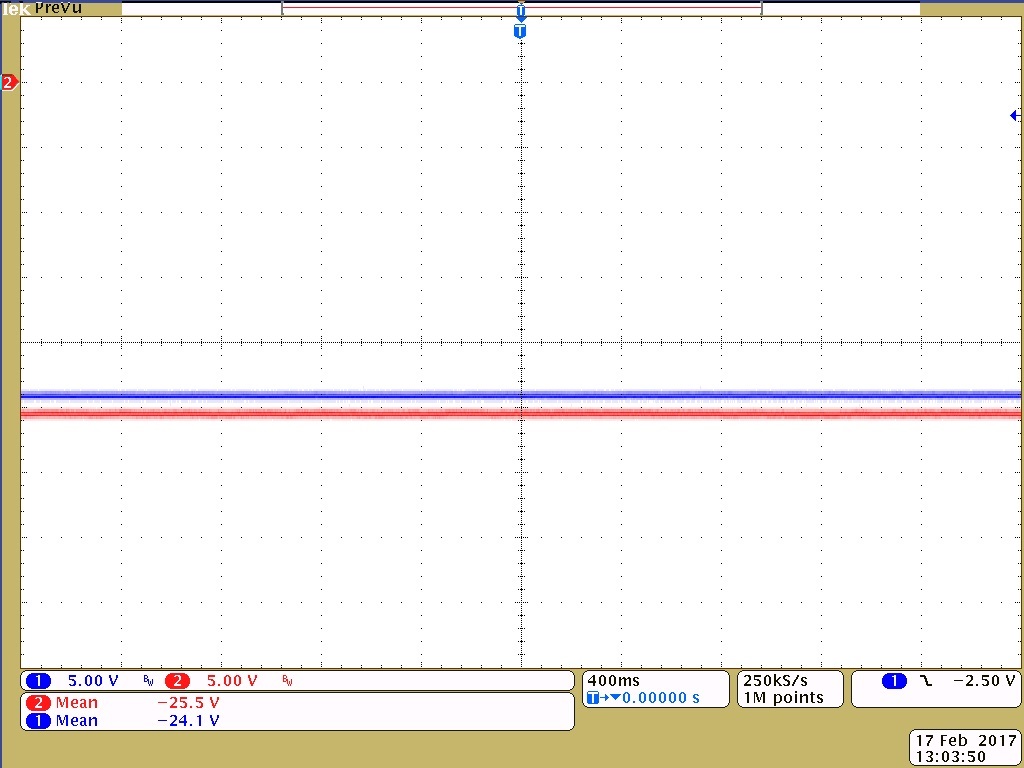

TPS7A4701和3301设置为+/-24VDC输出(根据数据表),Traco TVN 5-2425的LDO输入,微调至+/-25Vdc。 LDO输入信号噪声+波纹: < 2mVpp。

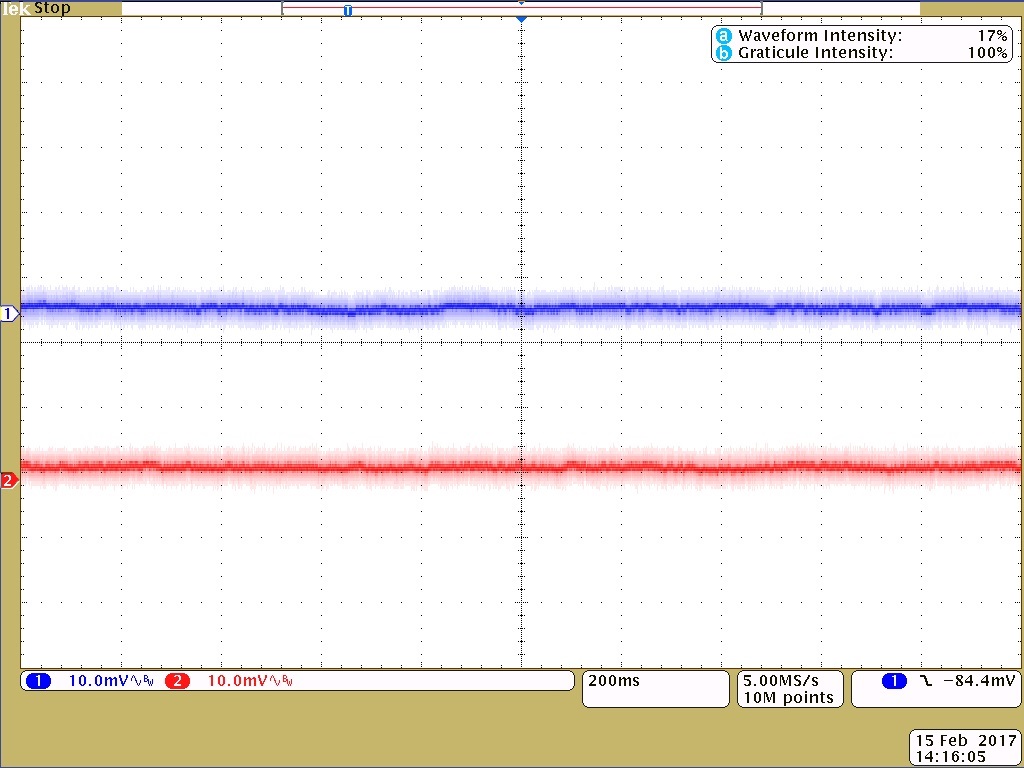

无负载,开路示波器测量。

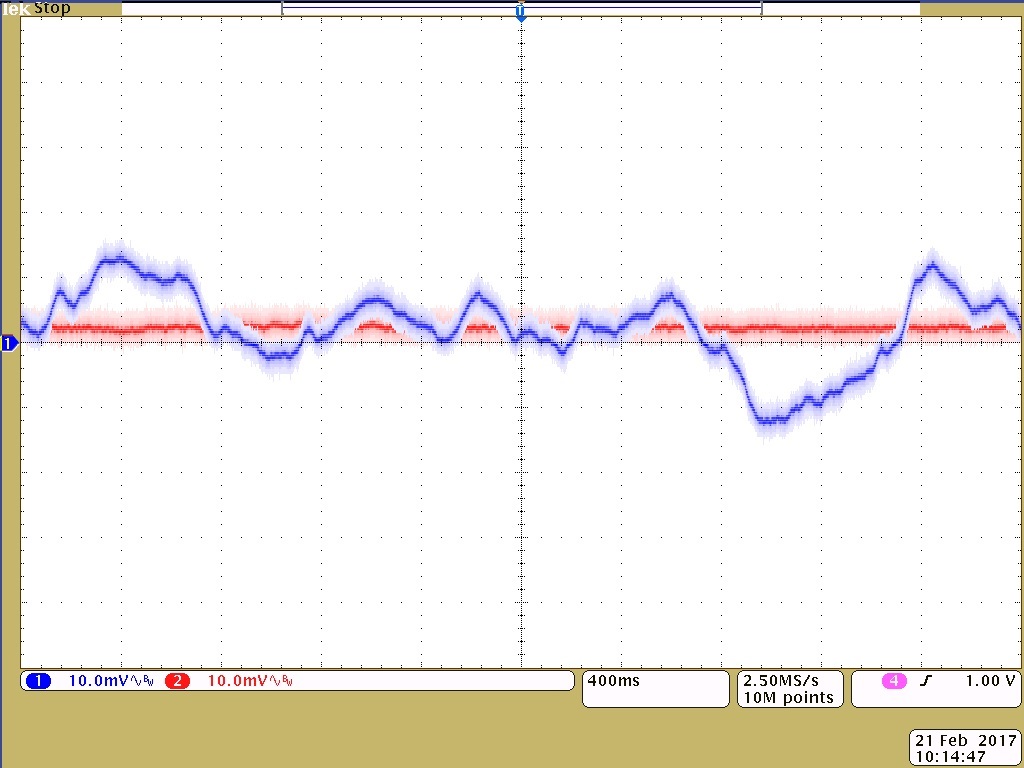

当PCB通电-> Day #1 -> LDO信号测量值@ J15/J16引脚1:顶部跟踪-蓝色:-24VDC输出, 交流耦合,底部跟踪:红色+24VDC输出,交流耦合。 两个滑轨噪音低。

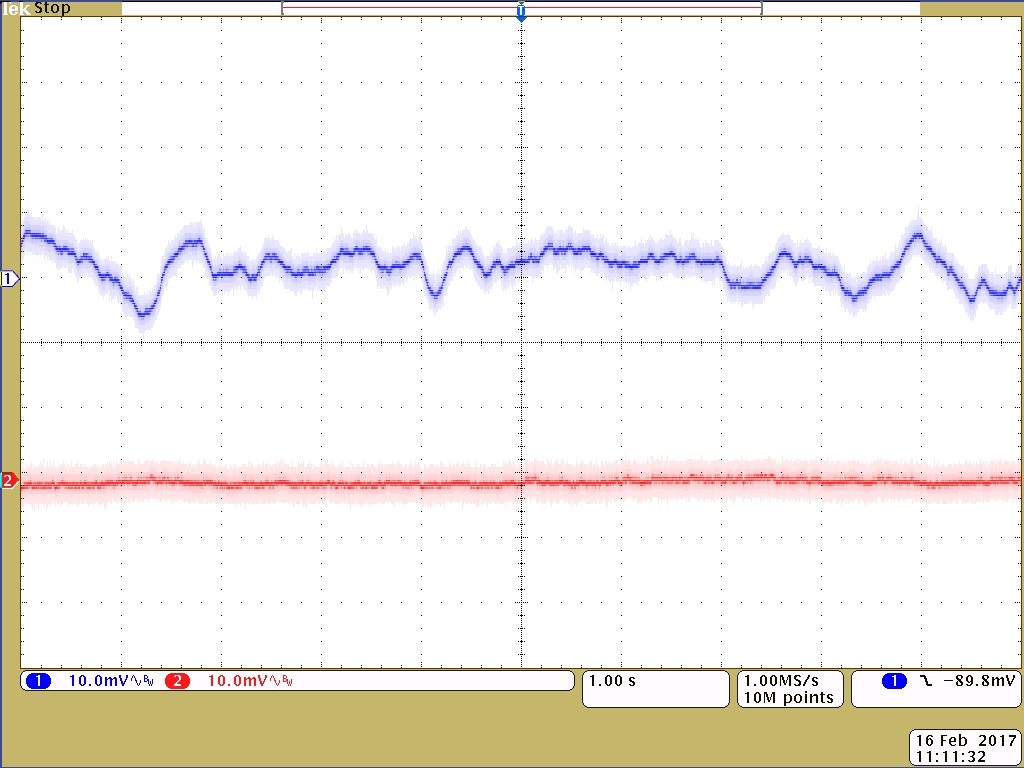

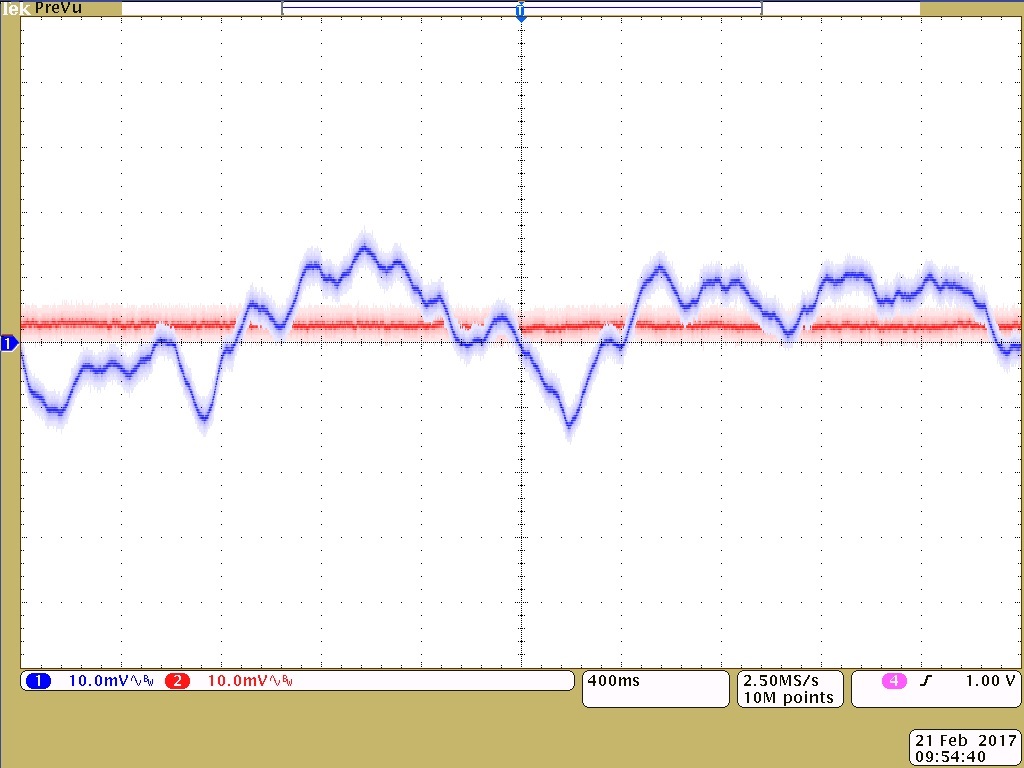

PCB在实验室中运行一夜: 24VDC LDO输出的噪声明显更高。 电源已回收。 不变。 在三(3)个相同的原型上重复。 结果相同。

印刷电路板布局如下所示,顶部组件和第1层布线。 第2层上的接地平面。

如有任何帮助,我们将不胜感激。